[CMSC 411 Home] |

[Syllabus] |

[Project] |

[VHDL resource] |

[Homework 1-6] |

[Homework 7-12]

[Files] |

CS411 ALU for project Part1

library IEEE;

use IEEE.std_logic_1164.all;

entity equal6 is -- basically a 6-bit op code compare

port(inst : in std_logic_vector(5 downto 0);

test : in std_logic_vector(5 downto 0);

equal : out std_logic);

end entity equal6;

architecture circuits of equal6 is

begin -- circuits

equal <= (inst(0) xnor test(0)) and

(inst(1) xnor test(1)) and

(inst(2) xnor test(2)) and

(inst(3) xnor test(3)) and

(inst(4) xnor test(4)) and

(inst(5) xnor test(5));

end architecture circuits; -- of equal6

library IEEE;

use IEEE.std_logic_1164.all;

entity alu_32 is

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

signal cin : std_logic := '0';

signal cout : std_logic;

begin -- schematic

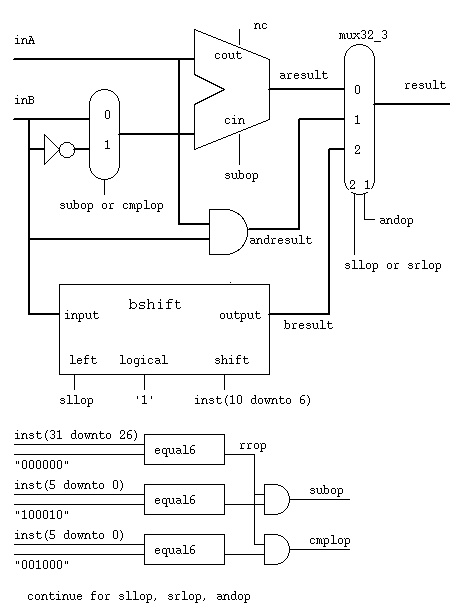

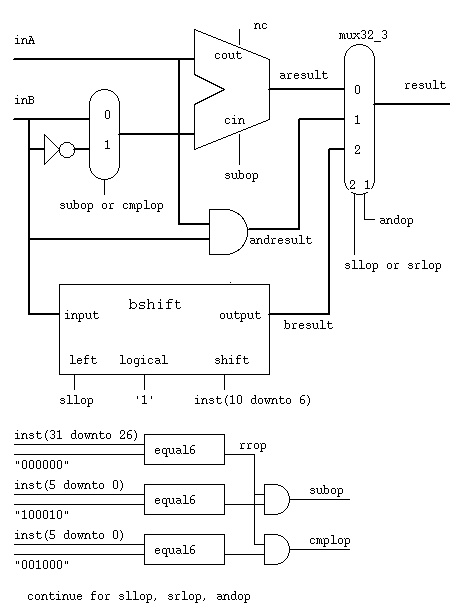

adder: entity WORK.add32 port map(a => inA,

b => inB, -- change

cin => cin, -- change

sum => result, -- change

cout => cout);

-- bsh: entity WORK.bshift port map(left => sllop,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

-- r1: entity WORK.equal6 port map(inst => inst(31 downto 26),

test => "000000",

equal => rrop);

-- ...

-- a1: subop <= rrop and ????;

-- ...

end architecture schematic; -- of alu_32

library IEEE;

use IEEE.std_logic_1164.all;

entity equal6 is -- basically a 6-bit op code compare

port(inst : in std_logic_vector(5 downto 0);

test : in std_logic_vector(5 downto 0);

equal : out std_logic);

end entity equal6;

architecture circuits of equal6 is

begin -- circuits

equal <= (inst(0) xnor test(0)) and

(inst(1) xnor test(1)) and

(inst(2) xnor test(2)) and

(inst(3) xnor test(3)) and

(inst(4) xnor test(4)) and

(inst(5) xnor test(5));

end architecture circuits; -- of equal6

library IEEE;

use IEEE.std_logic_1164.all;

entity alu_32 is

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

signal cin : std_logic := '0';

signal cout : std_logic;

begin -- schematic

adder: entity WORK.add32 port map(a => inA,

b => inB, -- change

cin => cin, -- change

sum => result, -- change

cout => cout);

-- bsh: entity WORK.bshift port map(left => sllop,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

-- r1: entity WORK.equal6 port map(inst => inst(31 downto 26),

test => "000000",

equal => rrop);

-- ...

-- a1: subop <= rrop and ????;

-- ...

end architecture schematic; -- of alu_32

library IEEE;

use IEEE.std_logic_1164.all;

entity equal6 is -- basically a 6-bit op code compare

port(inst : in std_logic_vector(5 downto 0);

test : in std_logic_vector(5 downto 0);

equal : out std_logic);

end entity equal6;

architecture circuits of equal6 is

begin -- circuits

equal <= (inst(0) xnor test(0)) and

(inst(1) xnor test(1)) and

(inst(2) xnor test(2)) and

(inst(3) xnor test(3)) and

(inst(4) xnor test(4)) and

(inst(5) xnor test(5));

end architecture circuits; -- of equal6

library IEEE;

use IEEE.std_logic_1164.all;

entity alu_32 is

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

signal cin : std_logic := '0';

signal cout : std_logic;

begin -- schematic

adder: entity WORK.add32 port map(a => inA,

b => inB, -- change

cin => cin, -- change

sum => result, -- change

cout => cout);

-- bsh: entity WORK.bshift port map(left => sllop,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

-- r1: entity WORK.equal6 port map(inst => inst(31 downto 26),

test => "000000",

equal => rrop);

-- ...

-- a1: subop <= rrop and ????;

-- ...

end architecture schematic; -- of alu_32

library IEEE;

use IEEE.std_logic_1164.all;

entity equal6 is -- basically a 6-bit op code compare

port(inst : in std_logic_vector(5 downto 0);

test : in std_logic_vector(5 downto 0);

equal : out std_logic);

end entity equal6;

architecture circuits of equal6 is

begin -- circuits

equal <= (inst(0) xnor test(0)) and

(inst(1) xnor test(1)) and

(inst(2) xnor test(2)) and

(inst(3) xnor test(3)) and

(inst(4) xnor test(4)) and

(inst(5) xnor test(5));

end architecture circuits; -- of equal6

library IEEE;

use IEEE.std_logic_1164.all;

entity alu_32 is

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

signal cin : std_logic := '0';

signal cout : std_logic;

begin -- schematic

adder: entity WORK.add32 port map(a => inA,

b => inB, -- change

cin => cin, -- change

sum => result, -- change

cout => cout);

-- bsh: entity WORK.bshift port map(left => sllop,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

-- r1: entity WORK.equal6 port map(inst => inst(31 downto 26),

test => "000000",

equal => rrop);

-- ...

-- a1: subop <= rrop and ????;

-- ...

end architecture schematic; -- of alu_32