<- previous index next ->

Multiplication and division are taught in elementary school, yet

they are still being worked on for computer applications.

The earliest computers just provided add and subtract with

conditional Branch, leaving the programmer to write multiply

and divide subroutines.

Early computers used bit-serial methods that required about

N squared clock times for multiplying or dividing N-bit numbers.

With a parallel adder, the time for multiply was reduced to

N/2 clock times (Booth algorithm) and division N clock times.

Todays computers use parallel, combinational, circuits for

multiply and divide. These circuits still take too long for

signals to propagate in one clock time. The combinational

circuits are "pipelined" so that a multiply or divide can be

completed every clock time.

Consider multiplying unsigned numbers 1010 * 1100 (10 times 12)

Using a hand method would produce:

1010

* 1100

---------

0000 <- think of the multiplier bit being "anded" with

0000 the multiplicand. A 1-bit "and" in digital logic

1010 is like a 1-bit "multiply".

1010

---------

01111000 4-bits times 4-bits produces an 8-bit product

When adding by hand, we can add the middle columns four bits and

produce a sum bit and possibly a carry. In hardware the number

of input bits is fixed. From the previous lecture, we could use

four 4-bit adders with additional "and" gates to do the multiply.

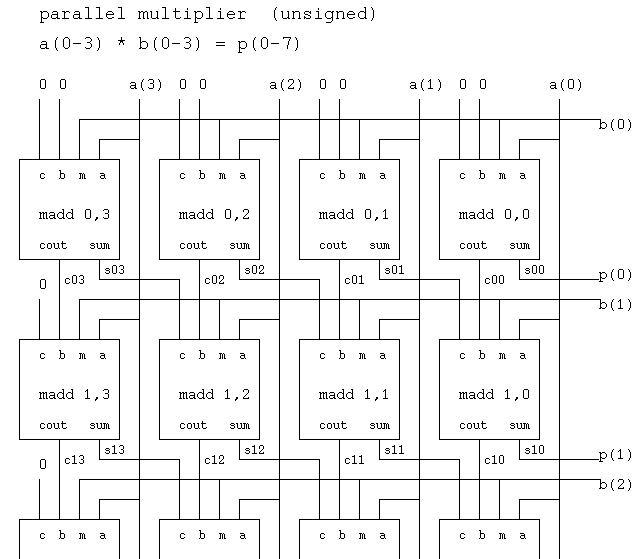

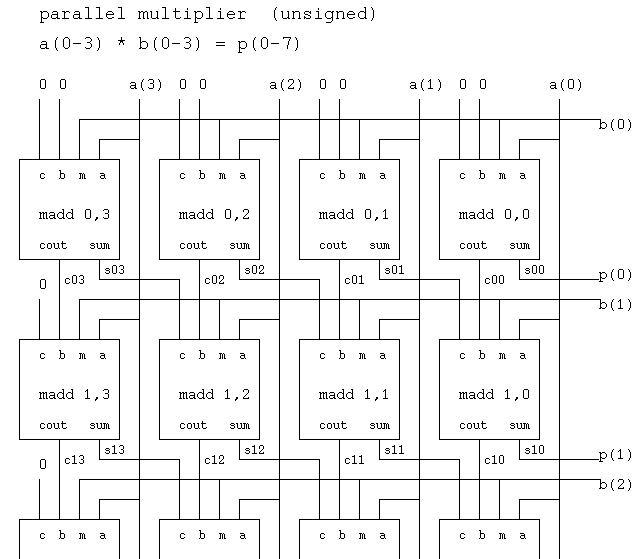

A better design incorporates the "and" gate to do a 1-bit multiply

inside the previous lectures full adder. With this single building

block, that is easy to replicate many times, we get the following

parallel multiplier design.

The 4-bit by 4-bit multiply to produce an 8-bit unsigned product is

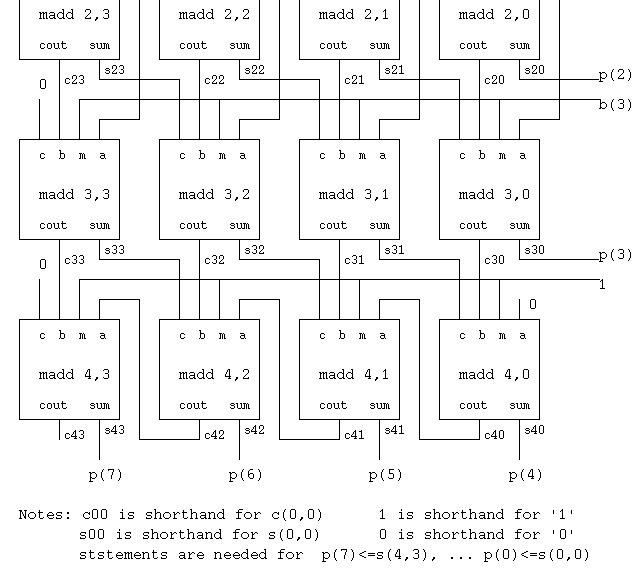

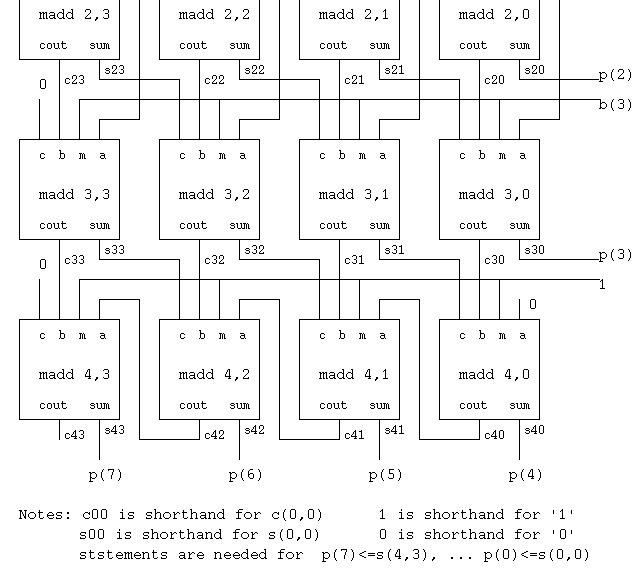

The component madd circuit is

The component madd circuit is

The VHDL source code is pmul4.vhdl

The VHDL test driver is pmul4_test.vhdl

The VHDL output is pmul4_test.out

The Cadence run file is pmul4_test.run

The partial Makefile is Makefile.pmul4_test

Notice that the only component used to build the multiplier

is "madd" and some uses of "madd" have constants as inputs.

It is technology dependent whether the same circuit is used

or specialized, minimized, circuits are substituted.

Division is performed by using subtraction. A sample unsigned binary

division of an 8-bit dividend by a 4-bit divisor that produces

a 4-bit quotient and 4-bit remainder is:

1010 <- quotient

/---------

1100/ 01111011 <- dividend

-1100

-----

0110

-0000

------

1101

-1100

------

0011

-0000

-----

0011 <- remainder

With a parallel adder and a double length register, serial division

can be performed. Conventional division requires a trial subtraction

and possibly a restore of the partial remainder. A non restoring

serial division requires N clock times for a N-bit divisor.

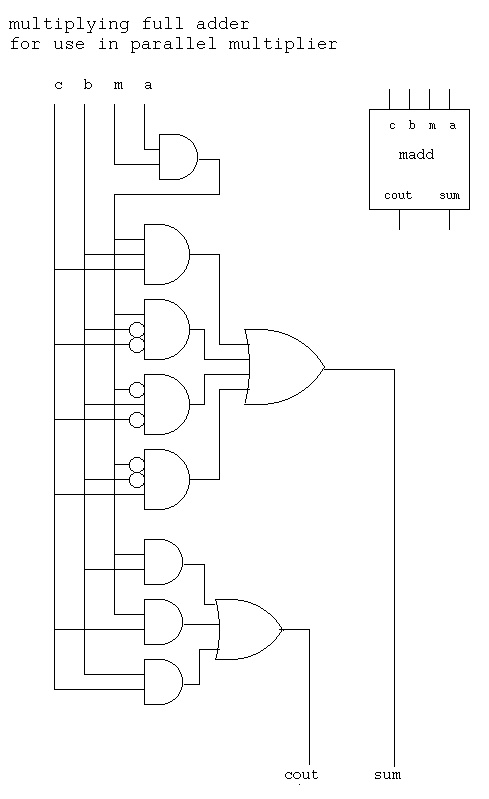

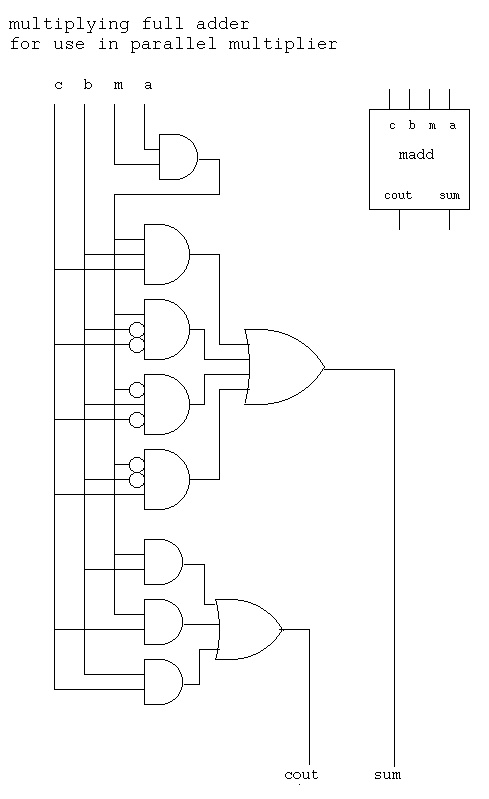

The schematic for a parallel 8-bit dividend divided by 4-bit divisor

to produce an 4-bit quotient and 4-bit remainder is:

The VHDL source code is pmul4.vhdl

The VHDL test driver is pmul4_test.vhdl

The VHDL output is pmul4_test.out

The Cadence run file is pmul4_test.run

The partial Makefile is Makefile.pmul4_test

Notice that the only component used to build the multiplier

is "madd" and some uses of "madd" have constants as inputs.

It is technology dependent whether the same circuit is used

or specialized, minimized, circuits are substituted.

Division is performed by using subtraction. A sample unsigned binary

division of an 8-bit dividend by a 4-bit divisor that produces

a 4-bit quotient and 4-bit remainder is:

1010 <- quotient

/---------

1100/ 01111011 <- dividend

-1100

-----

0110

-0000

------

1101

-1100

------

0011

-0000

-----

0011 <- remainder

With a parallel adder and a double length register, serial division

can be performed. Conventional division requires a trial subtraction

and possibly a restore of the partial remainder. A non restoring

serial division requires N clock times for a N-bit divisor.

The schematic for a parallel 8-bit dividend divided by 4-bit divisor

to produce an 4-bit quotient and 4-bit remainder is:

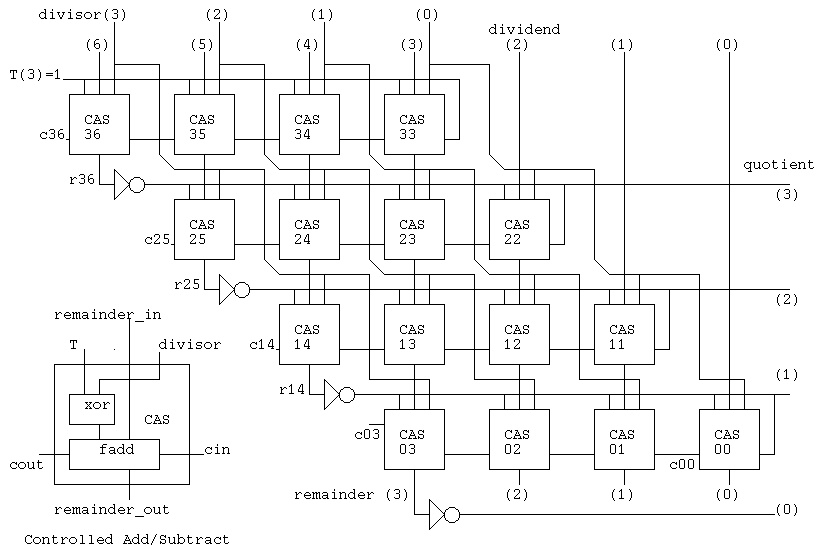

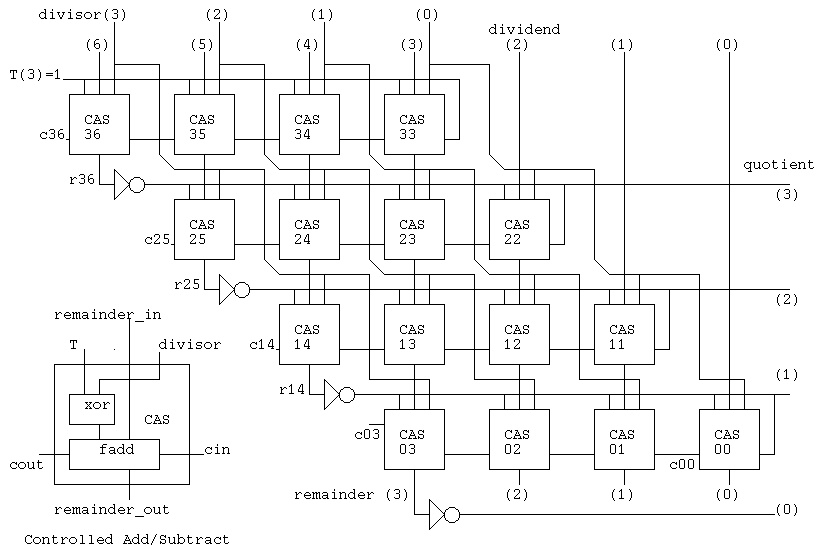

Notice that the building block is similar to the 'madd' component

in the parallel multiplier. The 'cas' component is the same full

adder with an additional xor gate.

The VHDL test driver is divcas4_test.vhdl

The VHDL output is divcas4_test.out

The Cadence run file is divcas4_test.run

The partial Makefile is Makefile.divcas4_test

Divide can create on overflow condition. This is typically handled by

separate logic in order to keep the main circuit neat. There is a

one bit preshift of the dividend in the manual, serial and parallel

division. Thus, no dividend bit number seven appears on the parallel

schematic.

Notice that the building block is similar to the 'madd' component

in the parallel multiplier. The 'cas' component is the same full

adder with an additional xor gate.

The VHDL test driver is divcas4_test.vhdl

The VHDL output is divcas4_test.out

The Cadence run file is divcas4_test.run

The partial Makefile is Makefile.divcas4_test

Divide can create on overflow condition. This is typically handled by

separate logic in order to keep the main circuit neat. There is a

one bit preshift of the dividend in the manual, serial and parallel

division. Thus, no dividend bit number seven appears on the parallel

schematic.

<- previous index next ->

The component madd circuit is

The component madd circuit is

The VHDL source code is pmul4.vhdl

The VHDL test driver is pmul4_test.vhdl

The VHDL output is pmul4_test.out

The Cadence run file is pmul4_test.run

The partial Makefile is Makefile.pmul4_test

Notice that the only component used to build the multiplier

is "madd" and some uses of "madd" have constants as inputs.

It is technology dependent whether the same circuit is used

or specialized, minimized, circuits are substituted.

Division is performed by using subtraction. A sample unsigned binary

division of an 8-bit dividend by a 4-bit divisor that produces

a 4-bit quotient and 4-bit remainder is:

1010 <- quotient

/---------

1100/ 01111011 <- dividend

-1100

-----

0110

-0000

------

1101

-1100

------

0011

-0000

-----

0011 <- remainder

With a parallel adder and a double length register, serial division

can be performed. Conventional division requires a trial subtraction

and possibly a restore of the partial remainder. A non restoring

serial division requires N clock times for a N-bit divisor.

The schematic for a parallel 8-bit dividend divided by 4-bit divisor

to produce an 4-bit quotient and 4-bit remainder is:

The VHDL source code is pmul4.vhdl

The VHDL test driver is pmul4_test.vhdl

The VHDL output is pmul4_test.out

The Cadence run file is pmul4_test.run

The partial Makefile is Makefile.pmul4_test

Notice that the only component used to build the multiplier

is "madd" and some uses of "madd" have constants as inputs.

It is technology dependent whether the same circuit is used

or specialized, minimized, circuits are substituted.

Division is performed by using subtraction. A sample unsigned binary

division of an 8-bit dividend by a 4-bit divisor that produces

a 4-bit quotient and 4-bit remainder is:

1010 <- quotient

/---------

1100/ 01111011 <- dividend

-1100

-----

0110

-0000

------

1101

-1100

------

0011

-0000

-----

0011 <- remainder

With a parallel adder and a double length register, serial division

can be performed. Conventional division requires a trial subtraction

and possibly a restore of the partial remainder. A non restoring

serial division requires N clock times for a N-bit divisor.

The schematic for a parallel 8-bit dividend divided by 4-bit divisor

to produce an 4-bit quotient and 4-bit remainder is:

Notice that the building block is similar to the 'madd' component

in the parallel multiplier. The 'cas' component is the same full

adder with an additional xor gate.

The VHDL test driver is divcas4_test.vhdl

The VHDL output is divcas4_test.out

The Cadence run file is divcas4_test.run

The partial Makefile is Makefile.divcas4_test

Divide can create on overflow condition. This is typically handled by

separate logic in order to keep the main circuit neat. There is a

one bit preshift of the dividend in the manual, serial and parallel

division. Thus, no dividend bit number seven appears on the parallel

schematic.

Notice that the building block is similar to the 'madd' component

in the parallel multiplier. The 'cas' component is the same full

adder with an additional xor gate.

The VHDL test driver is divcas4_test.vhdl

The VHDL output is divcas4_test.out

The Cadence run file is divcas4_test.run

The partial Makefile is Makefile.divcas4_test

Divide can create on overflow condition. This is typically handled by

separate logic in order to keep the main circuit neat. There is a

one bit preshift of the dividend in the manual, serial and parallel

division. Thus, no dividend bit number seven appears on the parallel

schematic.