<- previous index next ->

Standard decimal and binary multiplication could look like:

234 01010 multiplicand

x 121 x 00011 x multiplier

------ -------- --------------

234 01010 product

468 01010

234 00000

------ 00000

028314 00000

| ----------

| 0000011110 5-bits times 5-bits gives a 10-bit product,

| in a computer leading zeros are kept.

|

3-digits times 3-digits gives a 6-digit product, yet in

decimal, we do not write the leading zeros.

We have covered how computer adders work and how they are built.

Exactly two numbers are added to produce one sum, thus the binary

multiply above needs to be rewritten as:

01010

x 00011

----------

001010 -- multiplier LSB anded with multiplicand

+ 01010 -- multiplier bit-1 anded with multiplicand

-----

0011110 -- partial sum, bottom bit passed down

+ 00000 -- multiplier bit-2 anded with multiplicand

-----

00011110 -- partial sum, bottom two bits passed down

+ 00000 -- multiplier bit-3 anded with multiplicand

-----

000011110 -- partial sum, bottom three bits passed down

+ 00000 -- multiplier bit-4 anded with multiplicand

-----

0000011110 -- final product, four bits passed down

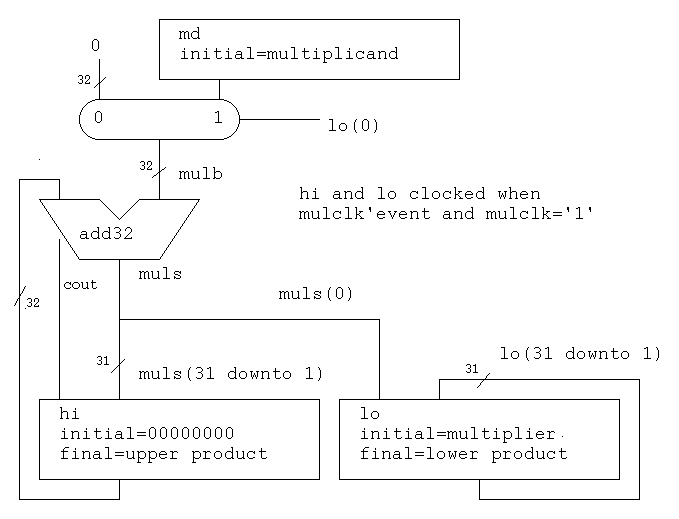

Thus, by this simple method, with a 5-bit unsigned multiplier, there

are four additions needed. A circuit that uses one adder and performs

serial multiplication follows directly. This design chose to use a

multiplexor rather than an 'and' operation to select the multiplicand

or zero.

How a register works

The VHDL code that represents the above circuit is:

mula <= hi;

mulb <= md when (lo(0)='1') else x"00000000" after 50 ps;

adder:entity WORK.add32 port map(mula, mulb, '0', muls, cout);

hi <= cout & muls(31 downto 1) when mulclk'event and mulclk='1';

lo <= muls(0) & lo(31 downto 1) when mulclk'event and mulclk='1';

The signal "mulclk" runs for the number of clock cycles that

their are bits in the multiplier, 32 for this example. For

simplicity of design, zero is added in the first step. Note that

"cout" is used when loading the "hi" register. The shifting is

accomplished by wire routing.

The VHDL test source code is mul_ser.vhdl

The output from the test is mul_ser.out

P.S. The above was an introduction, never use that method or circuit.

A serial multiplier can be built using only half as many clock cycles.

We use the technique developed by Mr. Booth. Two multiplier bits are

used each clock cycle. Only one add operation is needed each cycle,

yet the augend has several possible values as shown by the

multiplexor in the schematic and the table in the VHDL source code.

The VHDL code that represents the above circuit is:

mula <= hi;

mulb <= md when (lo(0)='1') else x"00000000" after 50 ps;

adder:entity WORK.add32 port map(mula, mulb, '0', muls, cout);

hi <= cout & muls(31 downto 1) when mulclk'event and mulclk='1';

lo <= muls(0) & lo(31 downto 1) when mulclk'event and mulclk='1';

The signal "mulclk" runs for the number of clock cycles that

their are bits in the multiplier, 32 for this example. For

simplicity of design, zero is added in the first step. Note that

"cout" is used when loading the "hi" register. The shifting is

accomplished by wire routing.

The VHDL test source code is mul_ser.vhdl

The output from the test is mul_ser.out

P.S. The above was an introduction, never use that method or circuit.

A serial multiplier can be built using only half as many clock cycles.

We use the technique developed by Mr. Booth. Two multiplier bits are

used each clock cycle. Only one add operation is needed each cycle,

yet the augend has several possible values as shown by the

multiplexor in the schematic and the table in the VHDL source code.

The VHDL test source code is bmul_ser.vhdl

The output from the test is bmul_ser.out

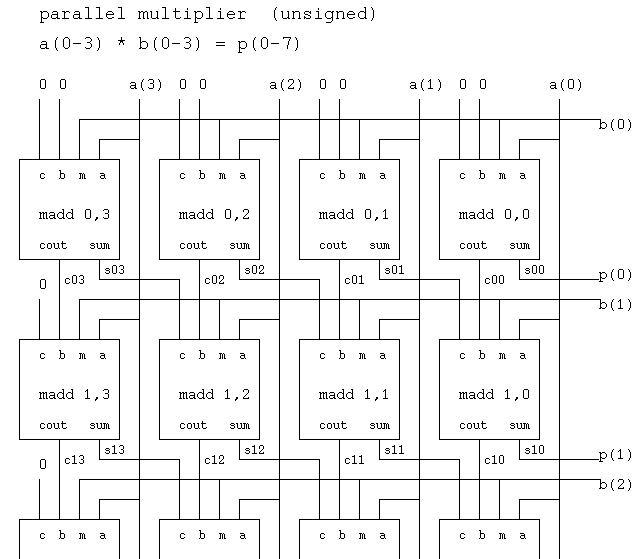

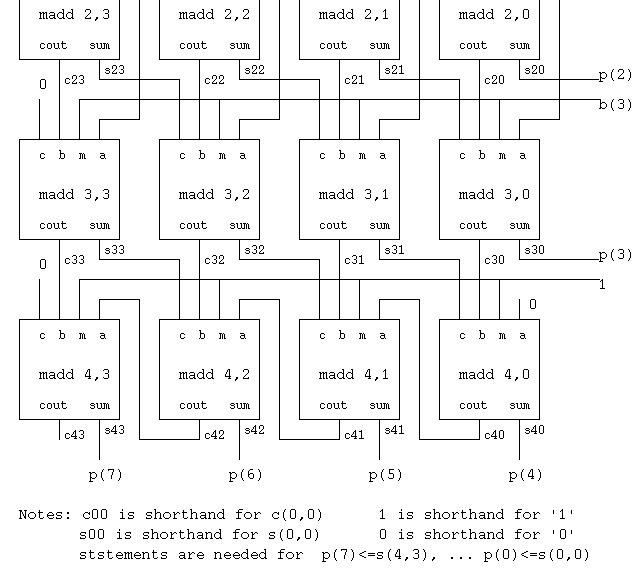

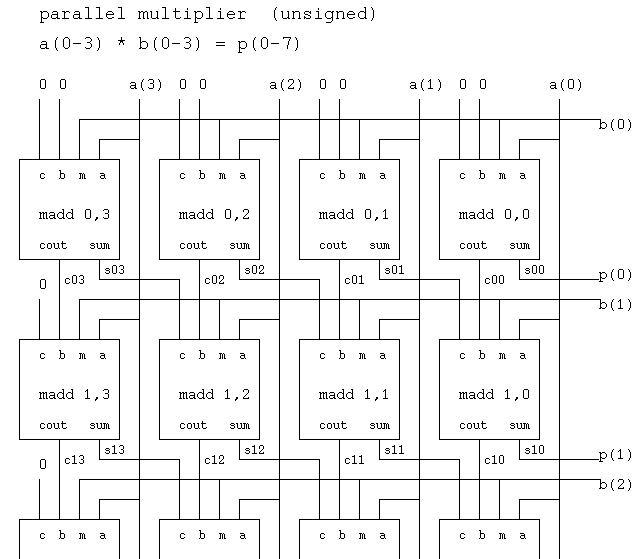

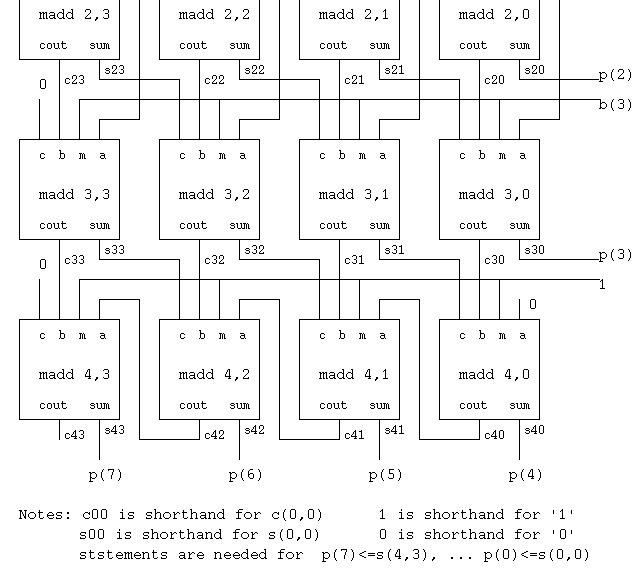

Next, parallel multiplication with a carry-save design.

Note there is no carry propagation except in the last stage.

The VHDL test source code is bmul_ser.vhdl

The output from the test is bmul_ser.out

Next, parallel multiplication with a carry-save design.

Note there is no carry propagation except in the last stage.

Some fancy VHDL using double subscripting and "generate".

pmul4.vhdl

A 32 bit design using an add32csa entity is:

Some fancy VHDL using double subscripting and "generate".

pmul4.vhdl

A 32 bit design using an add32csa entity is:

The VHDL entity for the carry-save multiplier is mul32c.vhdl

The VHDL test source code is mul32c_test.vhdl

The output from the test is mul32c_test.out

We can now combine the Booth multiplication technique to reduce the

number of stages in half, still using the parallel multiply.

The VHDL was written without a diagram, thus no schematic exists, yet.

The VHDL entity for the carry-save multiplier is bmul32.vhdl

The VHDL test source code is bmul32_test.vhdl

The output from the test is bmul32_test.out

Homework 5 is assigned

The VHDL entity for the carry-save multiplier is mul32c.vhdl

The VHDL test source code is mul32c_test.vhdl

The output from the test is mul32c_test.out

We can now combine the Booth multiplication technique to reduce the

number of stages in half, still using the parallel multiply.

The VHDL was written without a diagram, thus no schematic exists, yet.

The VHDL entity for the carry-save multiplier is bmul32.vhdl

The VHDL test source code is bmul32_test.vhdl

The output from the test is bmul32_test.out

Homework 5 is assigned

<- previous index next ->

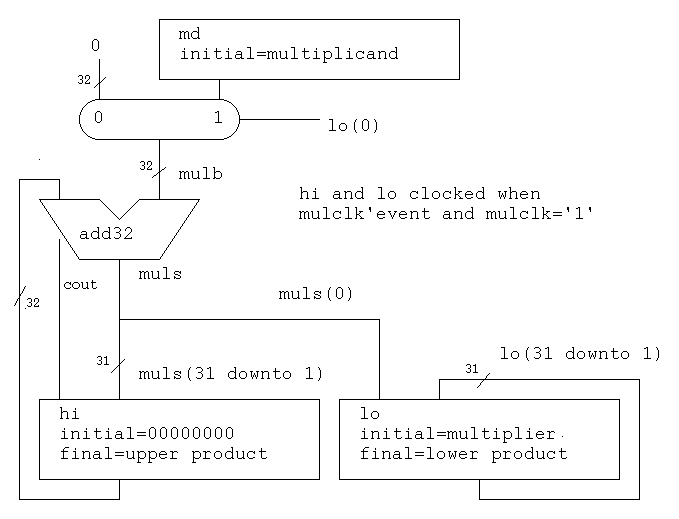

The VHDL code that represents the above circuit is:

mula <= hi;

mulb <= md when (lo(0)='1') else x"00000000" after 50 ps;

adder:entity WORK.add32 port map(mula, mulb, '0', muls, cout);

hi <= cout & muls(31 downto 1) when mulclk'event and mulclk='1';

lo <= muls(0) & lo(31 downto 1) when mulclk'event and mulclk='1';

The signal "mulclk" runs for the number of clock cycles that

their are bits in the multiplier, 32 for this example. For

simplicity of design, zero is added in the first step. Note that

"cout" is used when loading the "hi" register. The shifting is

accomplished by wire routing.

The VHDL test source code is mul_ser.vhdl

The output from the test is mul_ser.out

P.S. The above was an introduction, never use that method or circuit.

A serial multiplier can be built using only half as many clock cycles.

We use the technique developed by Mr. Booth. Two multiplier bits are

used each clock cycle. Only one add operation is needed each cycle,

yet the augend has several possible values as shown by the

multiplexor in the schematic and the table in the VHDL source code.

The VHDL code that represents the above circuit is:

mula <= hi;

mulb <= md when (lo(0)='1') else x"00000000" after 50 ps;

adder:entity WORK.add32 port map(mula, mulb, '0', muls, cout);

hi <= cout & muls(31 downto 1) when mulclk'event and mulclk='1';

lo <= muls(0) & lo(31 downto 1) when mulclk'event and mulclk='1';

The signal "mulclk" runs for the number of clock cycles that

their are bits in the multiplier, 32 for this example. For

simplicity of design, zero is added in the first step. Note that

"cout" is used when loading the "hi" register. The shifting is

accomplished by wire routing.

The VHDL test source code is mul_ser.vhdl

The output from the test is mul_ser.out

P.S. The above was an introduction, never use that method or circuit.

A serial multiplier can be built using only half as many clock cycles.

We use the technique developed by Mr. Booth. Two multiplier bits are

used each clock cycle. Only one add operation is needed each cycle,

yet the augend has several possible values as shown by the

multiplexor in the schematic and the table in the VHDL source code.

The VHDL test source code is bmul_ser.vhdl

The output from the test is bmul_ser.out

Next, parallel multiplication with a carry-save design.

Note there is no carry propagation except in the last stage.

The VHDL test source code is bmul_ser.vhdl

The output from the test is bmul_ser.out

Next, parallel multiplication with a carry-save design.

Note there is no carry propagation except in the last stage.

Some fancy VHDL using double subscripting and "generate".

pmul4.vhdl

A 32 bit design using an add32csa entity is:

Some fancy VHDL using double subscripting and "generate".

pmul4.vhdl

A 32 bit design using an add32csa entity is:

The VHDL entity for the carry-save multiplier is mul32c.vhdl

The VHDL test source code is mul32c_test.vhdl

The output from the test is mul32c_test.out

We can now combine the Booth multiplication technique to reduce the

number of stages in half, still using the parallel multiply.

The VHDL was written without a diagram, thus no schematic exists, yet.

The VHDL entity for the carry-save multiplier is bmul32.vhdl

The VHDL test source code is bmul32_test.vhdl

The output from the test is bmul32_test.out

Homework 5 is assigned

The VHDL entity for the carry-save multiplier is mul32c.vhdl

The VHDL test source code is mul32c_test.vhdl

The output from the test is mul32c_test.out

We can now combine the Booth multiplication technique to reduce the

number of stages in half, still using the parallel multiply.

The VHDL was written without a diagram, thus no schematic exists, yet.

The VHDL entity for the carry-save multiplier is bmul32.vhdl

The VHDL test source code is bmul32_test.vhdl

The output from the test is bmul32_test.out

Homework 5 is assigned