<- previous index next ->

This lecture uses Intel documentation on the X86-64 and IA-32 Architecture.

In principal IA-32 covers all Intel 80x86 machines up to and including

the Pentium 4.

In principal X86-64 covers all new Intel computers including HPC.

Stored locally in order to minimize network traffic.

First look over Appendix B. (This is a .pdf file that your

browser should activate acroread to display. Look on the left

for a table of contents and ultimately click on Appendix B.

(See meaning of "s" and "w". then look at the various "add" instructions.)

Intel IA-32 Instructions(pdf)

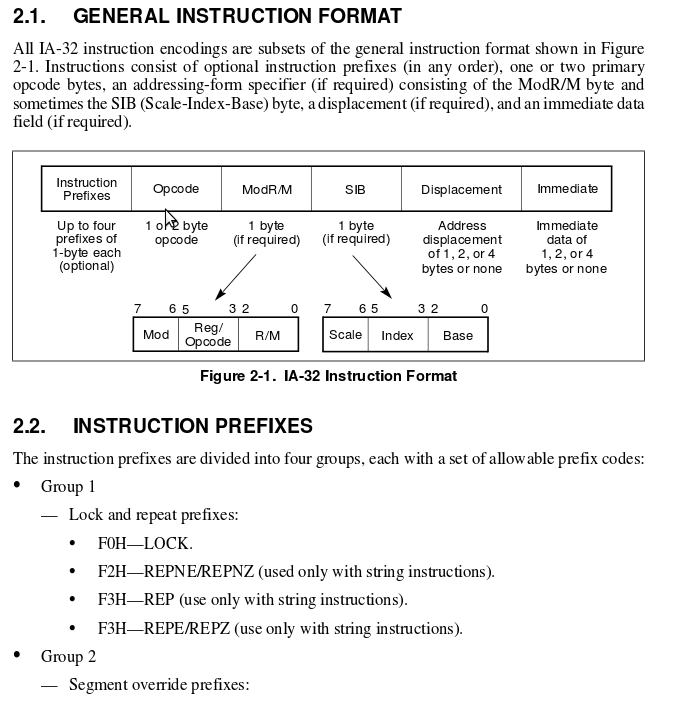

Note the "One Byte" opcodes. There are two tables with up to 256

instruction operation codes in each table.

Then move on to the "Two Byte" opcodes. The first opcode byte would

tell the CPU to look at the next byte to determine the operation code

for this instruction.

Sorry, the web and browsers and network are so darn slow,

I have included .png graphics of the pages:

>

>

intel64-ia32.pdf full 3439 pages 16.8MB including Instructions(pdf)

The X86-64 and IA-32 are CISC, Complex Instruction Set Computer.

This is in contrast to computer architectures such as the

Alpha, MIPS, PowerPC = Power4 = MAC G5, etc. that are

RISC, Reduced Instruction Set Computer. "Reduced" does not

mean, necessarily, fewer instructions. "Reduced" means

lower complexity and more regularity. Typically all instructions

are the same number of bytes. Four bytes equals 32 bits is the most

popular. Regular in the sense that all registers are general

purpose. Not like the IA-32 using EAX and EDX for multiply

and divide, X86-64 using RAX and RDX for multiply

All MIPS instructions are 32 bits, the 6 bit major opcode

allows 64 instructions and with the 6 bit minor opcode

there may be 4096 instructions. Just a few instruction are shown:

easier to program and simulate

Alpha another RISC architecture

intel64-ia32.pdf full 3439 pages 16.8MB including Instructions(pdf)

The X86-64 and IA-32 are CISC, Complex Instruction Set Computer.

This is in contrast to computer architectures such as the

Alpha, MIPS, PowerPC = Power4 = MAC G5, etc. that are

RISC, Reduced Instruction Set Computer. "Reduced" does not

mean, necessarily, fewer instructions. "Reduced" means

lower complexity and more regularity. Typically all instructions

are the same number of bytes. Four bytes equals 32 bits is the most

popular. Regular in the sense that all registers are general

purpose. Not like the IA-32 using EAX and EDX for multiply

and divide, X86-64 using RAX and RDX for multiply

All MIPS instructions are 32 bits, the 6 bit major opcode

allows 64 instructions and with the 6 bit minor opcode

there may be 4096 instructions. Just a few instruction are shown:

easier to program and simulate

Alpha another RISC architecture

<- previous index next ->

>

>

intel64-ia32.pdf full 3439 pages 16.8MB including Instructions(pdf)

The X86-64 and IA-32 are CISC, Complex Instruction Set Computer.

This is in contrast to computer architectures such as the

Alpha, MIPS, PowerPC = Power4 = MAC G5, etc. that are

RISC, Reduced Instruction Set Computer. "Reduced" does not

mean, necessarily, fewer instructions. "Reduced" means

lower complexity and more regularity. Typically all instructions

are the same number of bytes. Four bytes equals 32 bits is the most

popular. Regular in the sense that all registers are general

purpose. Not like the IA-32 using EAX and EDX for multiply

and divide, X86-64 using RAX and RDX for multiply

All MIPS instructions are 32 bits, the 6 bit major opcode

allows 64 instructions and with the 6 bit minor opcode

there may be 4096 instructions. Just a few instruction are shown:

easier to program and simulate

Alpha another RISC architecture

intel64-ia32.pdf full 3439 pages 16.8MB including Instructions(pdf)

The X86-64 and IA-32 are CISC, Complex Instruction Set Computer.

This is in contrast to computer architectures such as the

Alpha, MIPS, PowerPC = Power4 = MAC G5, etc. that are

RISC, Reduced Instruction Set Computer. "Reduced" does not

mean, necessarily, fewer instructions. "Reduced" means

lower complexity and more regularity. Typically all instructions

are the same number of bytes. Four bytes equals 32 bits is the most

popular. Regular in the sense that all registers are general

purpose. Not like the IA-32 using EAX and EDX for multiply

and divide, X86-64 using RAX and RDX for multiply

All MIPS instructions are 32 bits, the 6 bit major opcode

allows 64 instructions and with the 6 bit minor opcode

there may be 4096 instructions. Just a few instruction are shown:

easier to program and simulate

Alpha another RISC architecture