Lab 12: State Machine Project

Table of Contents

Objective

Learn to to design a statemachine, implement a state machine using logic gates, and verify the design using Verilog.

Lab Description

Almost all of the real world electronic systems are synthesized using

one or multiple finite state machines. This lab considers a finite

state machine controller for a 'coin to bills converter' machine. To

help needy children, a generous company has decided to offer $1 food

voucher for every 30 cents dropped into the machine. You are required to

design the state machine for the specifications provided below.

Specifications

The machine accepts only nickels (5 cents) and dimes (10 cents). The

output $1 food voucher should be dispensed when the total coin amount

reaches or exceeds 30 cents. If the amount exceeds 30 cents, the change

should be applied as credit towards next time the machine is used, i.e.,

no coins will be dispensed.

For the lab, there should be a 1 bit input which specifies the

following:

| Input | Coin |

|---|---|

| 0 | 5 Cents |

| 1 | 10 Cents |

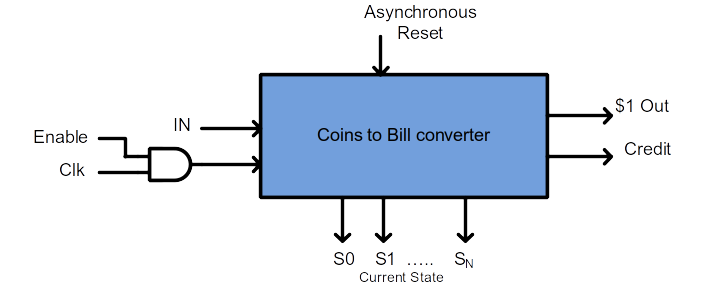

The diagram illustrates the input and output to the controller. The

asynchronous Reset input is to reset the state machine to its IDLE

state. As the food voucher is dispensed, the state machine should

reset itself to its initial (IDLE) state or a state that reflects the

amount to be credited (change).

There should be 2 outputs denoting the following:

-

1 bit -- Denotes the $1 out, which should be turned ON when the

input amount reaches or exceeds 30 cents. -

1 bit -- Denotes that the amount exceeded 30 cents and a credit is

applied towards future usage (You don't have to give the change).

You are to develop the state table and determine the number of bits "N" required for denoting the current state (and determine the number of

flip-flops).

To Do

-

The designed logic should have minimum number of gates, try to

simplify so that it will help in wiring. -

The design should be verified using Verilog with a test bench

demonstrating 3 examples of the working state machine. Details in

Verilog Section. -

The combinational logic in your sequential circuit should be

designed in '[structural model]{.underline}', using only 2-input

and/or 3-input gates.

Lab Report

- Make sure to explain your state diagram with neat titles, state

machine, inputs and outputs, K-Map / Quine-McCluskey reductions,

Boolean equations, circuit diagrams and all other details.

Submission

-

For this lab, main break down of the grades will be based on the

State Machine drawing and explanation for your design, your Verilog

code and the discussions on your lab -- what you have learned

from this lab. -

Add the state diagram of your design and a table specifying which

state corresponds to what value. Failure to do so will result in

losing points. -

Once the implementation is complete, TA will verify the state

machine with random inputs. -

The submission deadline for the report and Verilog files (including

testbench) is 12th May 2020, [10:00 PM EDT] Submit

all files using blackboard.

Please do NOT email your lab submissions to the TA or the instructor, unless you have a problem with for your blackboard account.

Important Notes

- This is an individual assignment; is not a group lab.

Provided Verilog and Sample Results

-

You will be using JK flip flops in this lab. Figure 1 shows the

Verilog code for Jk flip flop that you will be using. Note that flip

flop is negative edge sensitive. -

Code for generating a clock has been provided in Figure 2. Please

make sure to not change any settings in this code; namely initial

value of clk and its period. -

You are going to submit only one Verilog file;

named lab12.v -

All your modules must be in lab12.v file.

-

Your code needs to have helpful/meaningful comments.

-

Your testbench will have 3 sections/tests.

-

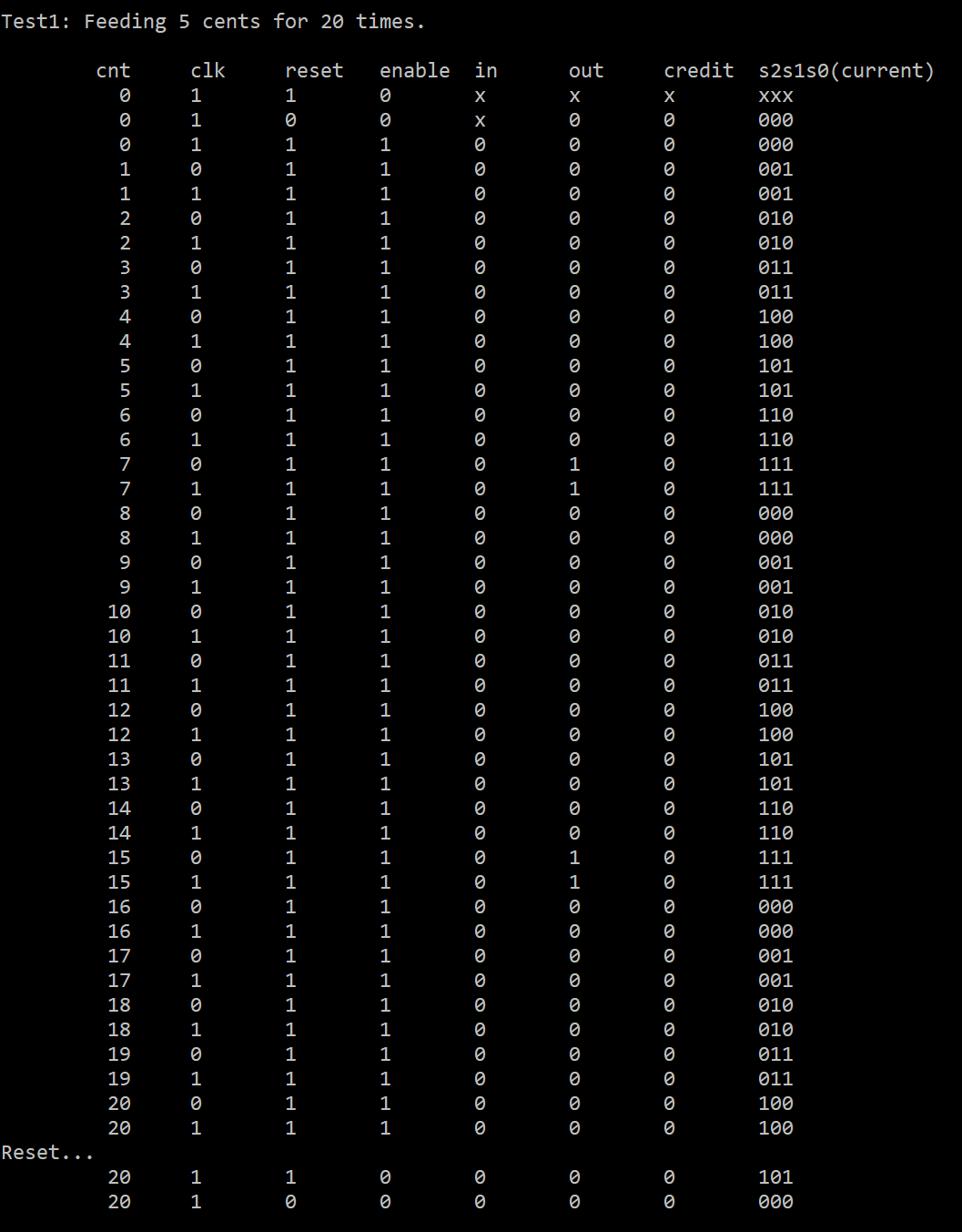

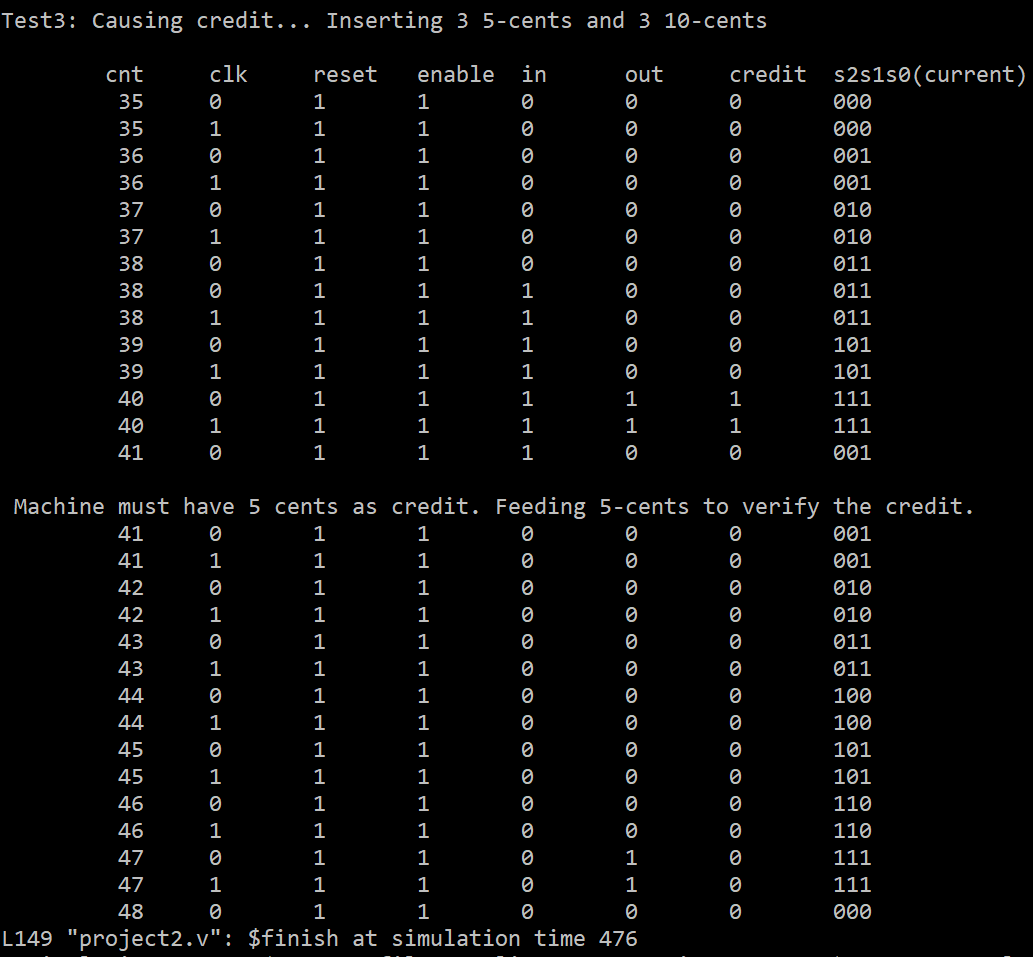

Test 1 will be feeding 5 cents only.

-

Test 2 will be feeding 10 cents only. This test also checks on

enable/disable input. -

Test 3, demonstrates the credit feature of circuit. It feeds

combination of 5 cents and 10 cents to force a credit. -

Between check tests mentioned above, a rest will be inserted to

clear states.

-

-

Your output should be like what has been presented in thefigure 4, 5 , and 6.

-

First column ("cnt") is clock's negative edge counter. It counts how

many times clock has been transitioned from 1 to 0 (negative edge).

The code for counter has been shown in figure 3. Variable counter is

type "integer". -

Second column, (clk) is main clock of circuit. If you check closely,

you will notice that when clk goes from 1 to 0, synchronized parts

of circuit change state (of course if they should) -

Last column (s2s1s0) shows current state of your state machine.

-

Codes are provided as a snapshot/picture on purpose to eliminate

formatting problems when you copy/paste it.