# CMSC 411 Computer Architecture

#### Lecture 23

### **Virtual Memory**

CMSC 411, Computer Architecture

## **Lecture's Overview**

#### Previous Lecture:

- Organization of main memory

- → Main memory performance issues

- → Memory interleaving

- Measuring and improving cache performance

- → Relationship between computer performance and cache

- ➔ Factors that affect cache performance

- ➔ Optimization techniques for cache performance

- Multi-level caches

- ➔ N-way set associative cache design

- ➔ Performance set of associate cache memory

#### **This Lecture:**

- Virtual Memory

- Integration of cache and virtual memory

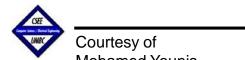

### **Memory Hierarchy**

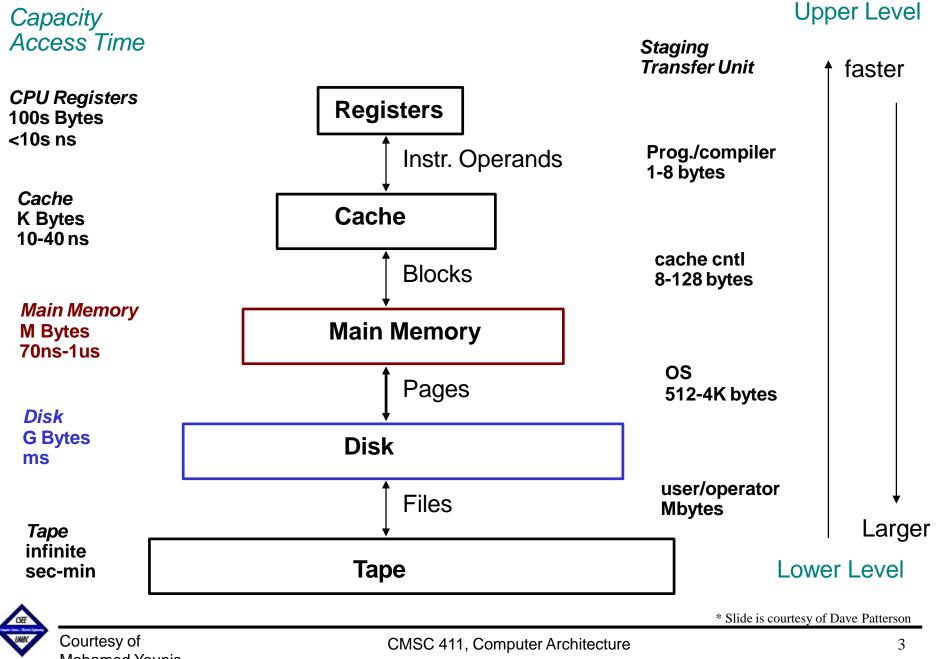

## **Virtual Memory**

- Using virtual addressing, main memory plays the role of cache for disks

- The virtual space is much larger than the physical memory space

- Physical main memory contains only the active portion of the virtual space

- Address space can be divided into fixed size (pages) or variable size (segments) blocks

#### <u>Advantages</u>

- ➔ Allows efficient and safe data sharing of memory among multiple programs

- Moves programming burdens of a small, limited amount of main memory

- Simplifies program loading and avoid the need for contiguous memory block

- allows programs to be loaded at any physical memory location

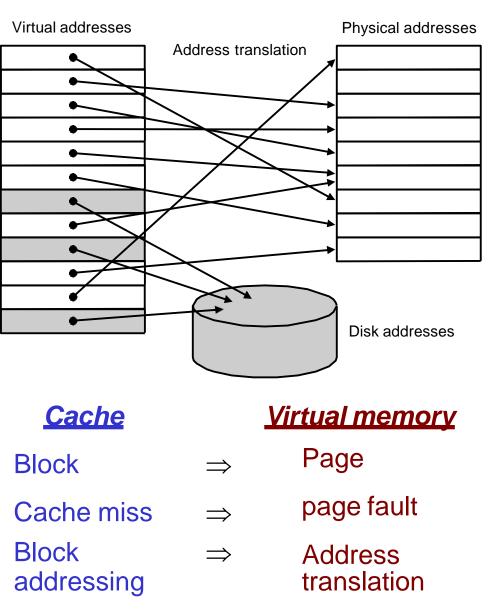

### **Virtual Addressing**

□ Page faults are costly and take millions of cycles to process (disks are slow)

#### Optimization Strategies:

- ➔ Pages should be large enough to amortize the high access time

- → Fully associative placement of pages reduces page fault rate

- → Software-based handling of page faults allows using clever page placement

- → Write-through technique can make writing very time consuming (use copy back)

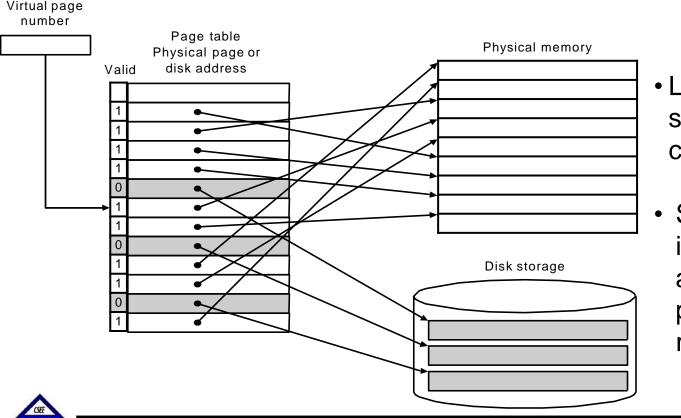

## Page Table

| Hardware supported                                           |            |                             | Page table re           | gister              |              |        |

|--------------------------------------------------------------|------------|-----------------------------|-------------------------|---------------------|--------------|--------|

|                                                              |            |                             |                         | Virtual address     |              |        |

| Page table:                                                  | 31 30 29   | 92827 ••                    | • • • • • • • • • • • • | ••••• 15 14 13 12   | 11 10 9 8 •• | 3210   |

| Resides in main memory                                       |            |                             | Virtual page            | number              | Page         | offset |

| One entry per virtual page                                   | N          | Valid                       | 20<br>Physical p        | age number          | `            | 12     |

| No tag is required since it covers all virtual pages         |            |                             |                         |                     |              |        |

| Point directly to physical page                              |            |                             |                         |                     |              |        |

| Table can be very large                                      | Page table | •                           |                         |                     |              |        |

| Operating sys. may maintain<br>one page table per process    |            |                             |                         |                     |              |        |

| A dirty bit is used to track<br>modified pages for copy back |            | n page is not<br>tin memory | ~                       | 18                  |              |        |

| Indicates whether the                                        | 29 28      | 8 27 •••••                  |                         | •••• 15 14 13 12 11 | 1098 ••      | 3210   |

| virtual page is in main memory or not                        |            |                             | Physical p              | age number          | Page         | offset |

| •                                                            |            |                             |                         | Physical address    |              |        |

#### **Page Faults**

A page fault happens when the valid bit of a virtual page is off

- A page fault generates an exception to be handled by the operating system to bring the page to main memory from a disk

- The operating system creates space for all pages on disk and keeps track of the location of pages in main memory and disk

Page location on disk can be stored in page table or in an auxiliary structure

CMSC 411, Computer Architecture

Courtesy of

- LRU page replacement strategy is the most commonly used

- Simplest LRU implementation uses a reference bit per page and periodically reset reference bits

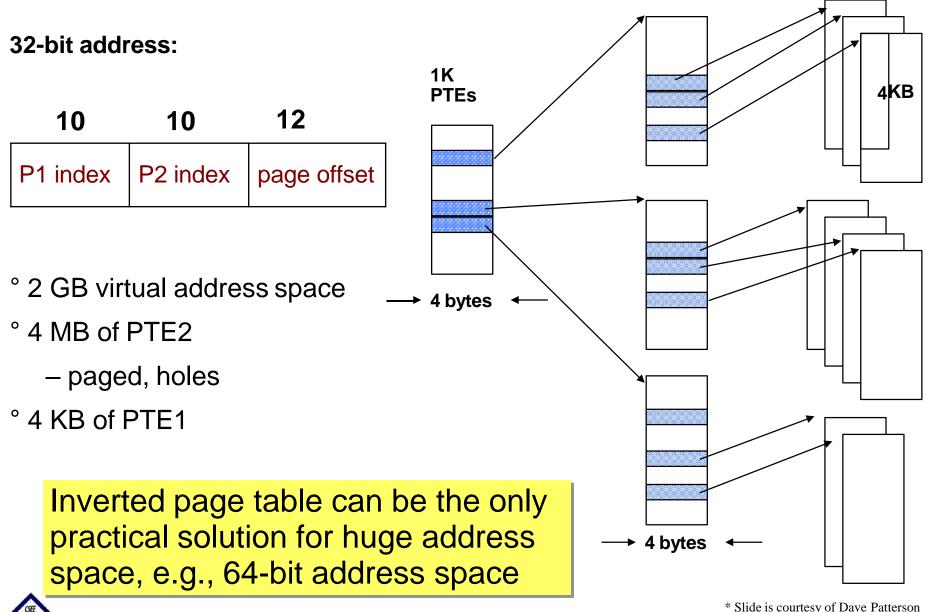

## **Optimizing Page Table Size**

With a 32-bit virtual address, 4-KB pages, and 4 bytes per page table entry:

Number of page table entries =

$$\frac{2^{32}}{2^{12}} = 2^{20}$$

Size of page table =  $2^{20}$  page table entries  $\times 2^2$  bytes page table entry = 4 MB

#### **Optimization techniques:**

- Keep bound registers to limit the size of page table for given process in order to avoid empty slots

- Store only physical pages and apply hashing function of the virtual address (inverted page table)

- > Allow paging of the page table, i.e. apply virtual addressing recursively

- Use multi-level page table to limit size of the table residing in main memory

$\succ$ Cache the most used pages  $\Rightarrow$  Translation Look-aside Buffer

### **Multi-Level Page Table**

Courtesy of

CMSC 411, Computer Architecture

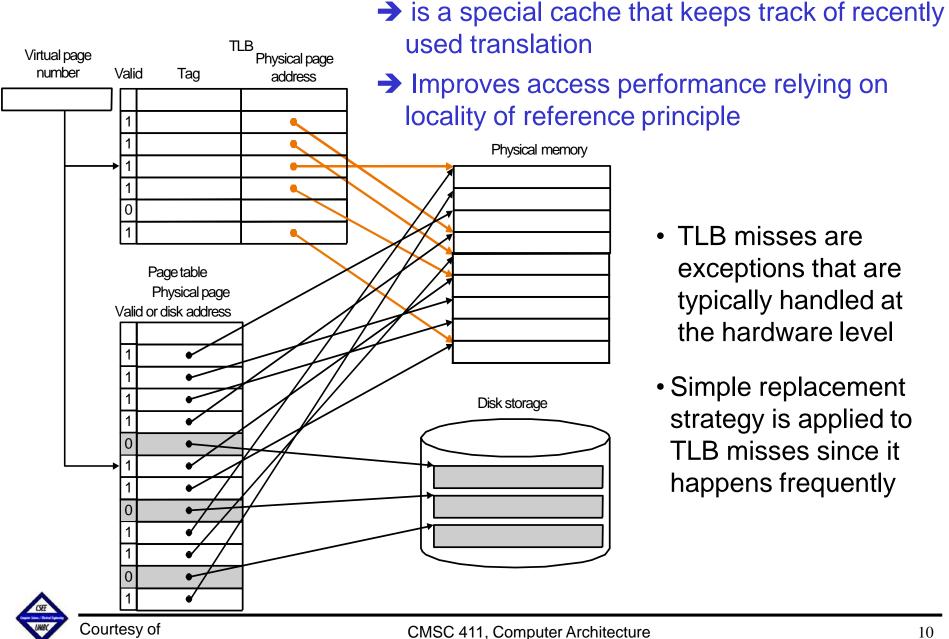

### **Translation Look-aside Buffer**

Mahana ad Maunala

- TLB misses are exceptions that are typically handled at the hardware level

- Simple replacement strategy is applied to TLB misses since it happens frequently

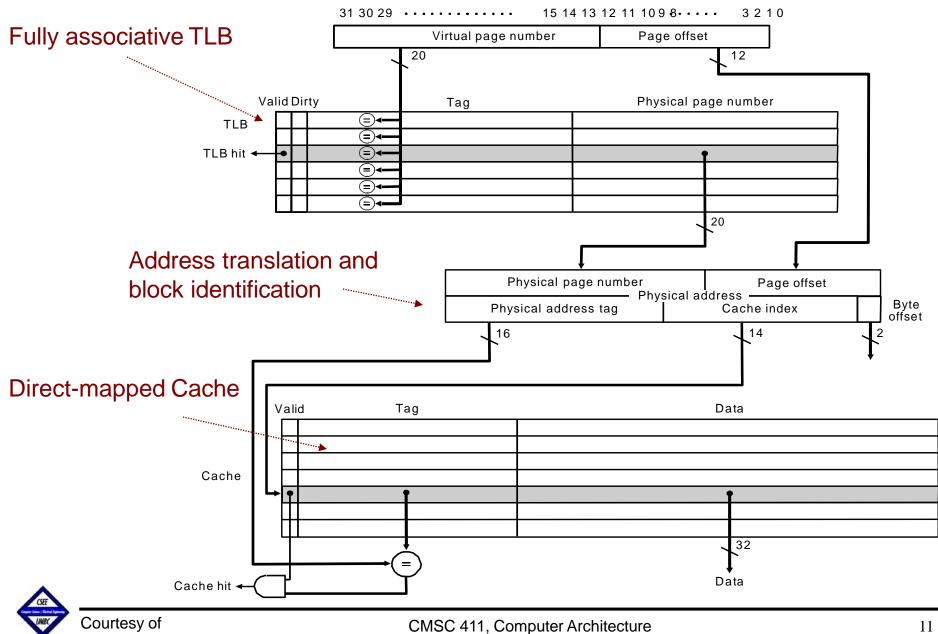

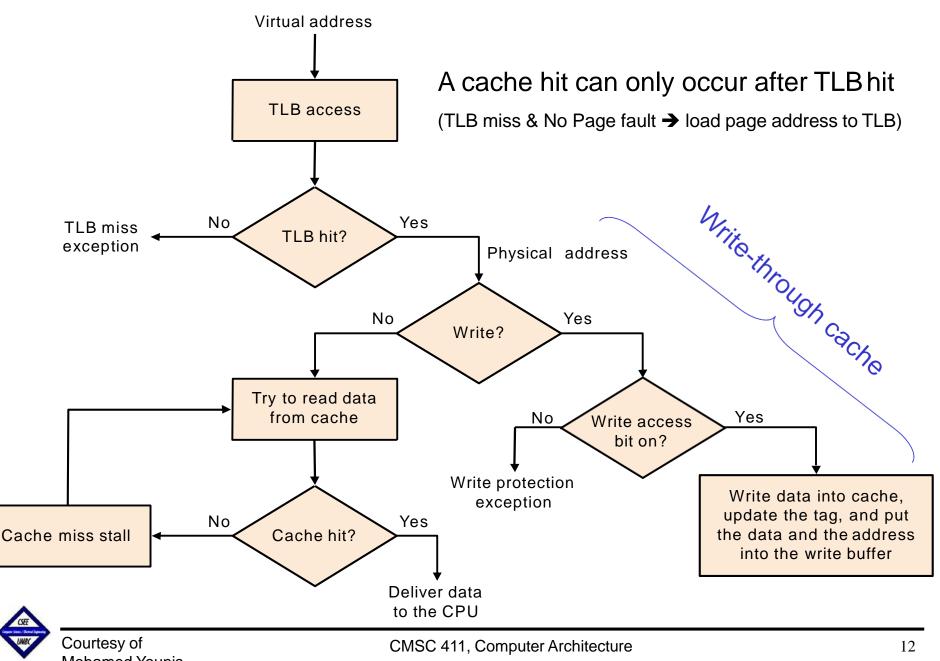

### **TLB and Cache in MIPS**

Virtual address

### **TLB and Cache in MIPS**

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| Cache | TLB  | Page<br>Table |

|-------|------|---------------|

| miss  | hit  | hit           |

| hit   | miss | hit           |

| miss  | miss | hit           |

| miss  | miss | miss          |

| miss  | hit  | miss          |

| hit   | hit  | miss          |

| hit   | miss | miss          |

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| Cache | TLB  | Page<br>Table | Possible? If so, under what condition                                 |  |

|-------|------|---------------|-----------------------------------------------------------------------|--|

| miss  | hit  | hit           | Possible, although the page table is never really checked if TLB hits |  |

| hit   | miss | hit           |                                                                       |  |

| miss  | miss | hit           |                                                                       |  |

| miss  | miss | miss          |                                                                       |  |

| miss  | hit  | miss          |                                                                       |  |

| hit   | hit  | miss          |                                                                       |  |

| hit   | miss | miss          |                                                                       |  |

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| Cache | TLB  | Page<br>Table | Possible? If so, under what condition                                 |

|-------|------|---------------|-----------------------------------------------------------------------|

| miss  | hit  | hit           | Possible, although the page table is never really checked if TLB hits |

| hit   | miss | hit           | TLB misses, but entry found in page table and data found in cache     |

| miss  | miss | hit           |                                                                       |

| miss  | miss | miss          |                                                                       |

| miss  | hit  | miss          |                                                                       |

| hit   | hit  | miss          |                                                                       |

| hit   | miss | miss          |                                                                       |

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| Cache | TLB  | Page<br>Table | Possible? If so, under what condition                                 |

|-------|------|---------------|-----------------------------------------------------------------------|

| miss  | hit  | hit           | Possible, although the page table is never really checked if TLB hits |

| hit   | miss | hit           | TLB misses, but entry found in page table and data found in cache     |

| miss  | miss | hit           | TLB misses, but entry found in page table and data misses in cache    |

| miss  | miss | miss          |                                                                       |

| miss  | hit  | miss          |                                                                       |

| hit   | hit  | miss          |                                                                       |

| hit   | miss | miss          |                                                                       |

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| Cache | TLB  | Page<br>Table | Possible? If so, under what condition                                 |

|-------|------|---------------|-----------------------------------------------------------------------|

| miss  | hit  | hit           | Possible, although the page table is never really checked if TLB hits |

| hit   | miss | hit           | TLB misses, but entry found in page table and data found in cache     |

| miss  | miss | hit           | TLB misses, but entry found in page table and data misses in cache    |

| miss  | miss | miss          | TLB misses and followed by page fault. Data must miss in cache        |

| miss  | hit  | miss          |                                                                       |

| hit   | hit  | miss          |                                                                       |

| hit   | miss | miss          |                                                                       |

|       |      | •             |                                                                       |

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| 3 hits |

|--------|

|        |

| che    |

| ache   |

| ne     |

| emory  |

|        |

| Π      |

|        |

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| TLB  | Page<br>Table                             | Possible? If so, under what condition                                 |

|------|-------------------------------------------|-----------------------------------------------------------------------|

| hit  | hit                                       | Possible, although the page table is never really checked if TLB hits |

| miss | hit                                       | TLB misses, but entry found in page table and data found in cache     |

| miss | hit                                       | TLB misses, but entry found in page table and data misses in cache    |

| miss | miss                                      | TLB misses and followed by page fault. Data must miss in cache        |

| hit  | miss                                      | Impossible: cannot have a translation in TLB if page is not in memory |

| hit  | miss                                      | Impossible: cannot have a translation in TLB if page is not in memory |

| miss | miss                                      |                                                                       |

|      | hit<br>miss<br>miss<br>miss<br>hit<br>hit | Tablehithitmisshitmisshitmissmisshitmisshitmisshitmiss                |

#### Possible exceptions:

Cache miss: referenced block not in cache and needs to be fetched from main memory

TLB miss: referenced page of virtual address needs to be checked in the page table

| Cache | TLB  | Page<br>Table | Possible? If so, under what condition                                 |

|-------|------|---------------|-----------------------------------------------------------------------|

| miss  | hit  | hit           | Possible, although the page table is never really checked if TLB hits |

| hit   | miss | hit           | TLB misses, but entry found in page table and data found in cache     |

| miss  | miss | hit           | TLB misses, but entry found in page table and data misses in cache    |

| miss  | miss | miss          | TLB misses and followed by page fault. Data must miss in cache        |

| miss  | hit  | miss          | Impossible: cannot have a translation in TLB if page is not in memory |

| hit   | hit  | miss          | Impossible: cannot have a translation in TLB if page is not in memory |

| hit   | miss | miss          | Impossible: data is not allowed in cache if page is not in memory     |

|       |      |               |                                                                       |

## **Memory Protection**

- □ It is always desirable to prevent a process from corrupting allocated memory space of other processes

- The processor must support processes in a non-privileged mode to avoid messing up memory protection

- Implementation can be by mapping independent virtual pages to separate physical pages

- □ Write protection bits would be included in the page table for authentication

- Sharing pages can be facilitated by the operating system through mapping virtual pages of different processes to same physical pages

- To enable the operating system to implement protection, the hardware must provide at least the following capabilities:

- → Support at least two modes of operations, one of them is a user mode

- Provide a portion of CPU state that a user process can read but not write, e.g. page pointer

- → Enable change of operation modes through special instructions

## Handling TLB Misses & Page Faults

#### □ <u>TLB Miss</u>: (hardware-based handling)

- → Check if the page is in memory (valid bit) --> update the TLB

- → Generate page fault exception if page is not in memory

#### □ <u>Page Fault</u>: (handled by operating system)

- ➔ Transfer control to the operating system

- → Save processor status: registers, program counter, page table pointer, etc.

- → Lookup the page table and find the location of the reference page on disk

- ➔ Choose a physical page to be replaced by the referenced page, if the candidate physical page is modified (dirty bit is set) the page needs to be written back

- → Start reading the referenced page from disk to the assigned physical page

- The processor needs to support "restarting" instructions in order to guarantee correct execution (easily supported in MIPS)

- The user process causing the page fault will be suspended by the operating system until the page is readily available in main memory

- Protection violations are handled by the operating system similarly but without automatic instruction restarting

## Conclusion

#### □ <u>Summary</u>

#### ➔ Virtual Memory

- Virtual addressing

- Address translation

#### ➔ Memory paging

- Page table

- Page faults

- Translation look-aside buffer

#### ➔ Memory-related exceptions

- Relationship between TLB, cache miss and page fault exceptions

- Handling of memory-related exceptions

#### ] <u>Next Lecture</u>

➔ Input/Output system

#### Read sections 5.4 in 5<sup>th</sup> Ed. of the textbook

Courtesy of