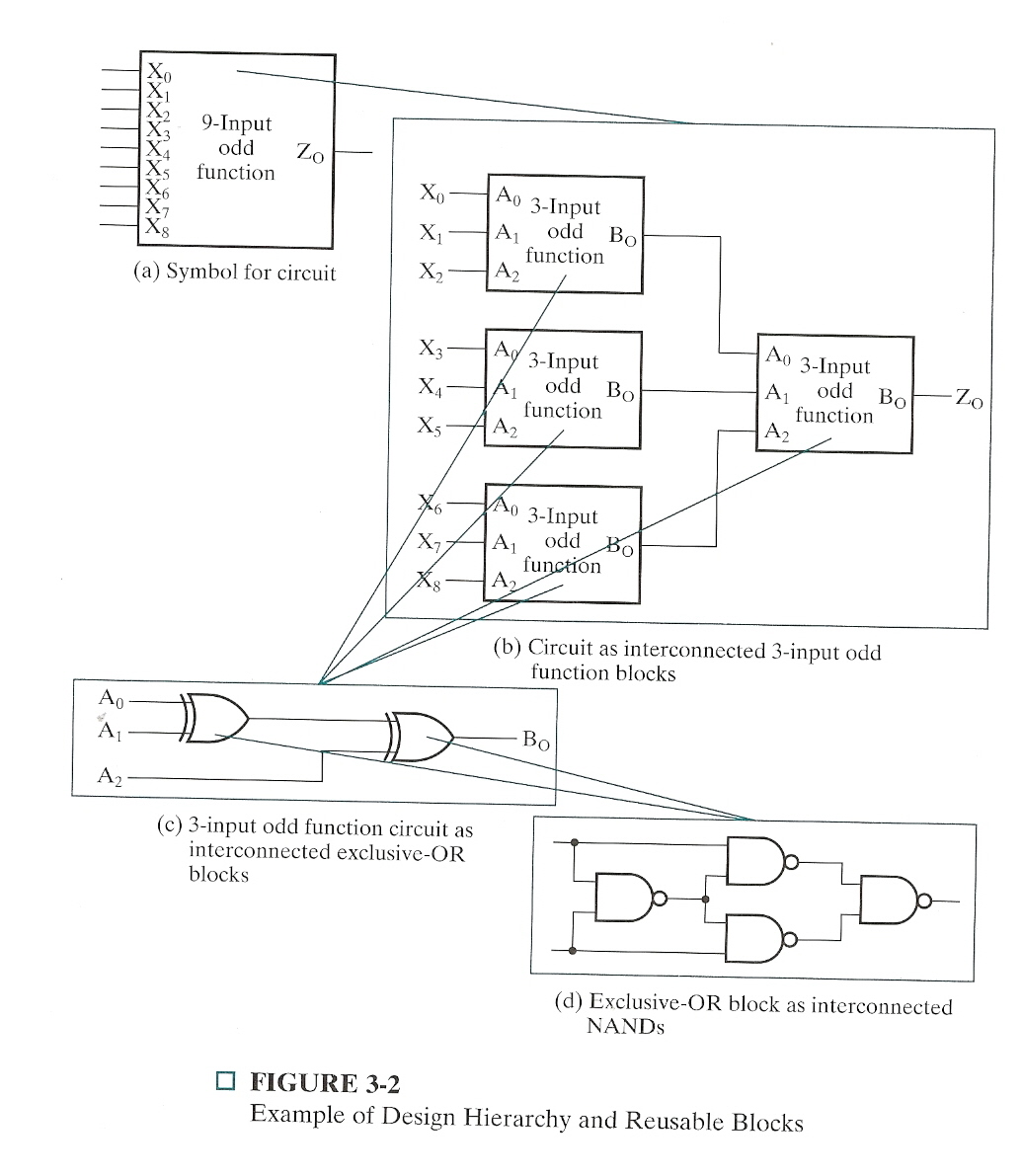

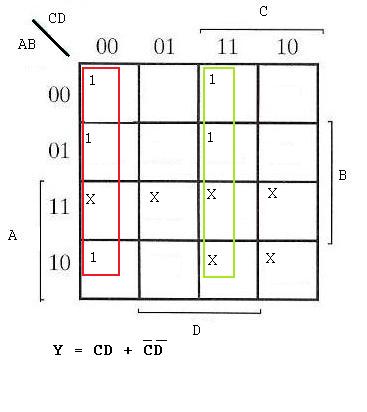

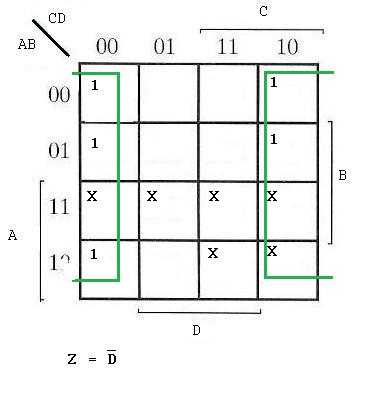

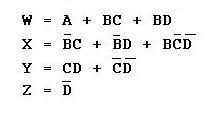

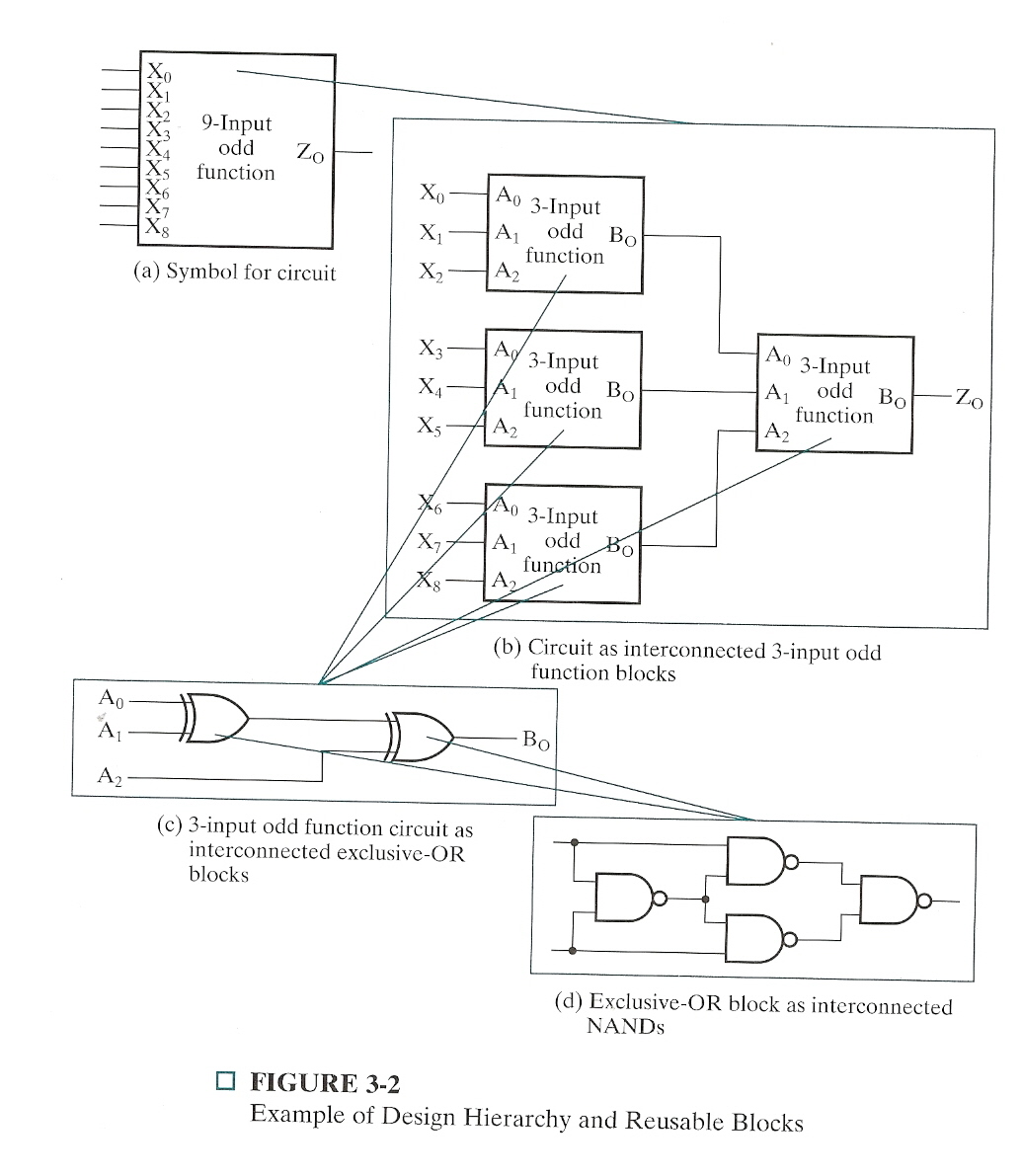

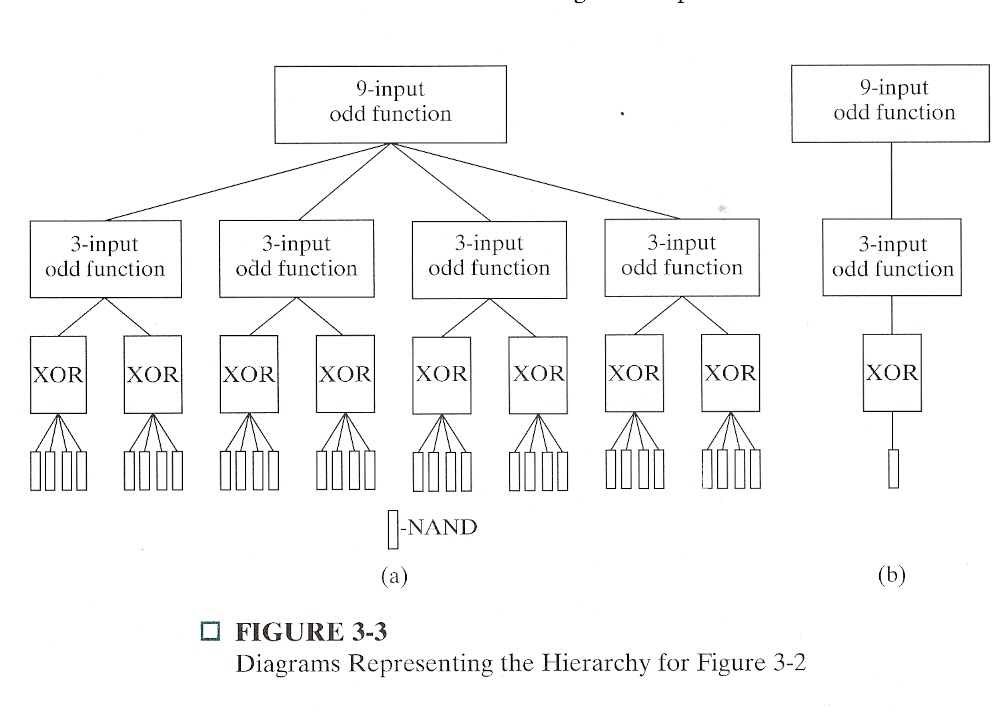

As in software, we have a requirements specification of some form. Assume we have a 9-Input odd function, showing if we have an odd

number of 1's in the input. One solution is to break it down into a set 3-Input odd functions that their result is feed into another 3-Input odd function.

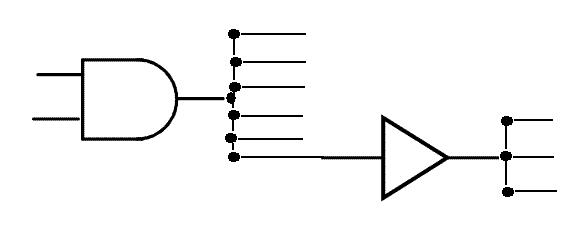

We can break that down into two XOR gates. Each XOR can then be broken down into a set of NANDs. This results in the following chart:

Logic and Computer Design Fundamentals, 3rd Ed., Mano and Kime, Prentice Hall, 2004, Page 90

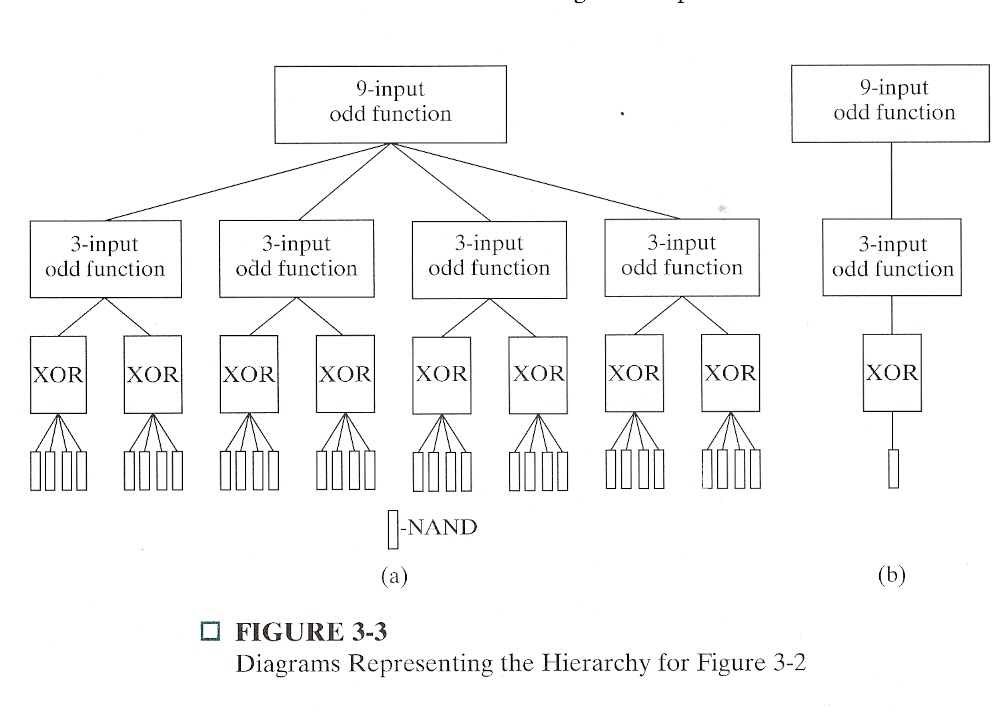

Another way to diagram this is:

Logic and Computer Design Fundamentals, 3rd Ed., Mano and Kime, Prentice Hall, 2004, Page 91

As you can see, the principles of top-down design and functional decomposition apply to hardware as well as software. The other software

principle here is reuse, by instantiating a good design again and again.