# Digital Logic VII: Memory Hierarchy CMSC 313 Sections 01, 02

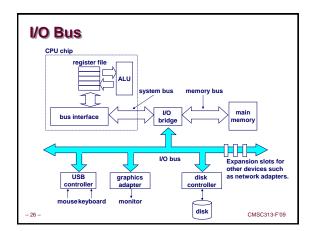

# Typical Bus Structure Connecting CPU and Memory A bus is a collection of parallel wires that carry address, data, and control signals. Buses are typically shared by multiple devices. CPU chip register file User the system bus memory bus memory bus bridge bus interface

4

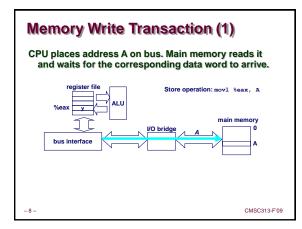

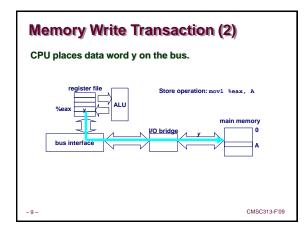

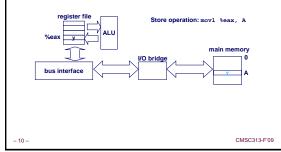

# Memory Write Transaction (3)

Main memory read data word y from the bus and stores it at address A.

#### Key features

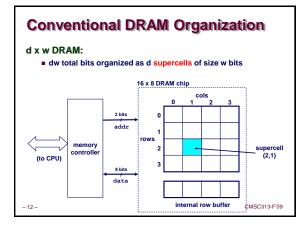

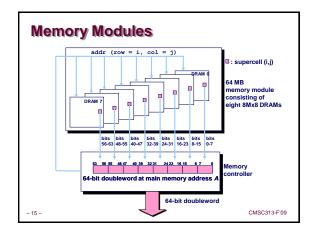

- RAM is packaged as a chip.

- Basic storage unit is a cell (one bit per cell).

- Multiple RAM chips form a memory.

#### Static RAM (SRAM)

- Each cell stores bit with a six-transistor circuit.

- Retains value indefinitely, as long as it is kept powered.

- Relatively insensitive to disturbances such as electrical noise.

CMSC313-F'09

Faster and more expensive than DRAM.

#### Dynamic RAM (DRAM)

- Each cell stores bit with a capacitor and transistor.

- Value must be refreshed every 10-100 ms.

- Sensitive to disturbances.

- Slower and cheaper than SRAM.

- 11 -

# **Nonvolatile Memories**

#### DRAM and SRAM are volatile memories

Lose information if powered off.

- Nonvolatile memories retain value even if powered off.

- Generic name is read-only memory (ROM).

- Misleading because some ROMs can be read and modified.

- Types of ROMs

- Programmable ROM (PROM)

Freeseable programmable ROM (FROM)

- Eraseable programmable ROM (EPROM)

Electrically eraseable PROM (EEPROM)

- Flash memory

#### Firmware

- Program stored in a ROM

- Boot time code, BIOS (basic input/ouput system)

CMSC313-F'09

• graphics cards, disk controllers.

- 16 -

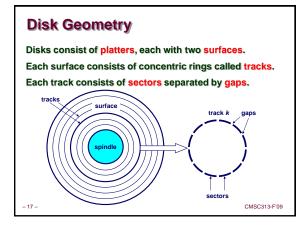

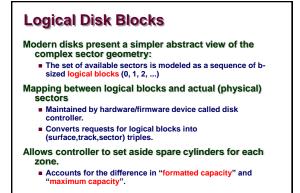

# **Disk Capacity**

- Capacity: maximum number of bits that can be stored. • Vendors express capacity in units of gigabytes (GB),

- where 1 GB = 10^9 bytes.

- Capacity is determined by these technology factors:

- Recording density (bits/in): number of bits that can be squeezed into a 1 inch segment of a track.

- Track density (tracks/in): number of tracks that can be squeezed into a 1 inch radial segment.

- Areal density (bits/in<sup>2</sup>): product of recording and track density.

- Modern disks partition tracks into disjoint subsets called recording zones

- Each track in a zone has the same number of sectors, determined by the circumference of innermost track.

CMSC313-F'09

- Each zone has a different number of sectors/track.

- 19 –

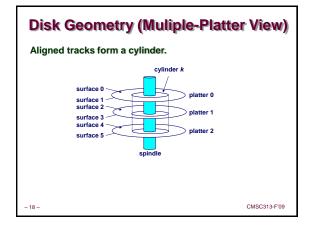

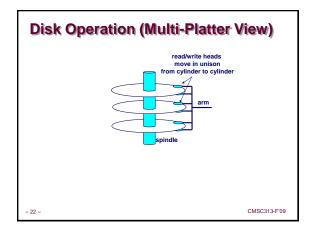

**Computing Disk Capacity** Capacity = (# bytes/sector) x (avg. # sectors/track) x (# tracks/surface) x (# surfaces/platter) x (# platters/disk) Example: 512 bytes/sector 300 sectors/track (on average) 20.000 tracks/surface 2 surfaces/platter 5 platters/disk Capacity = 512 x 300 x 20000 x 2 x 5 = 30,720,000,000 = 30.72 GB - 20 -CMSC313-F'09

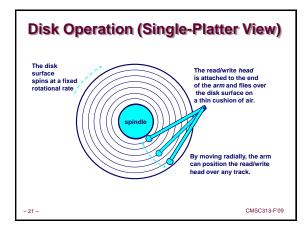

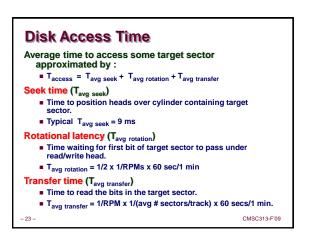

# **Disk Access Time Example**

Given:

- Rotational rate = 7,200 RPM

- Average seek time = 9 ms.

- Avg # sectors/track = 400.

Derived:

- 24 -

- Tavg rotation = 1/2 x (60 secs/7200 RPM) x 1000 ms/sec = 4 ms.

- Tavg transfer = 60/7200 RPM x 1/400 secs/track x 1000 ms/sec = 0.02 ms

- Taccess = 9 ms + 4 ms + 0.02 ms

Important points:

- Access time dominated by seek time and rotational latency.

- First bit in a sector is the most expensive, the rest are free.

- SRAM access time is about 4 ns/doubleword, DRAM about 60 ns

Disk is about 40,000 times slower than SRAM,

- 2,500 times slower then DRAM.

CMSC313-F'09

- 25 -

# Locality

Principle of Locality:

- Programs tend to reuse data and instructions near those they have used recently, or that were recently referenced themselves.

- Temporal locality: Recently referenced items are likely to be referenced in the near future.

- Spatial locality: Items with nearby addresses tend to be referenced close together in time.

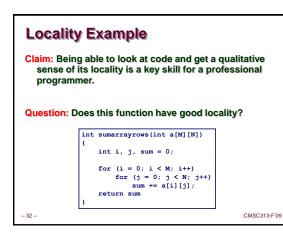

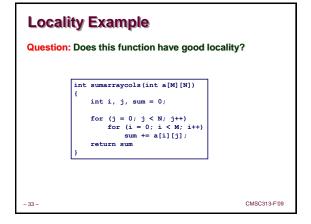

#### Locality Example:

Data

- 31 -

- sum = 0; for (i = 0; i < n; i++) sum += a[i]; return sum;

- Reference array elements in succession (stride-1 reference pattern): Spatial locality

- -Reference sum each iteration: Temporal locality

- Instructions

- Reference instructions in sequence: Spatial locality

- Cycle through loop repeatedly: Temporal locality CMSC313-F'09

##

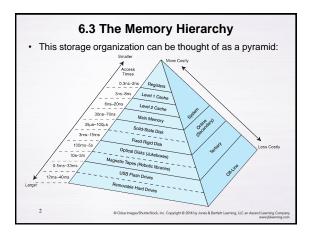

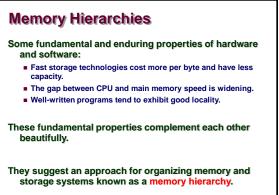

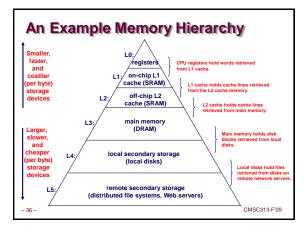

### Caches

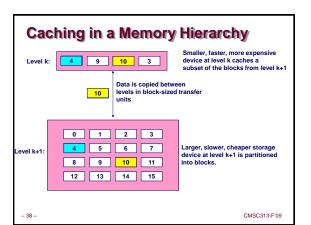

- Cache: A smaller, faster storage device that acts as a staging area for a subset of the data in a larger, slower device.

- Fundamental idea of a memory hierarchy:

- For each k, the faster, smaller device at level k serves as a cache for the larger, slower device at level k+1.

#### Why do memory hierarchies work?

- Programs tend to access the data at level k more often than they access the data at level k+1.

- Thus, the storage at level k+1 can be slower, and thus larger and cheaper per bit.

- Net effect: A large pool of memory that costs as much as the cheap storage near the bottom, but that serves data to programs at the rate of the fast storage near the top.

CMSC313-F'09

- 37 -

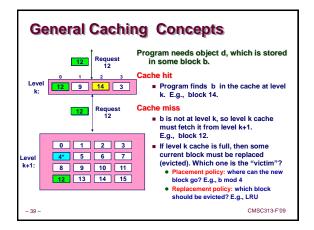

# **General Caching Concepts**

#### Types of cache misses:

- Cold (compulsary) miss

- Cold misses occur because the cache is empty.

- Conflict miss

40 -

- Most caches limit blocks at level k+1 to a small subset (sometimes a singleton) of the block positions at level k.

- E.g. Block i at level k+1 must be placed in block (i mod 4) at level k+1.

- Conflict misses occur when the level k cache is large enough, but multiple data objects all map to the same level k block.

- E.g. Referencing blocks 0, 8, 0, 8, 0, 8, ... would miss every time. • Capacity miss

- Occurs when the set of active cache blocks (working set) is larger than the cache.

| Examples of Caching in the Hierarchy |                         |                        |                     |                     |  |  |

|--------------------------------------|-------------------------|------------------------|---------------------|---------------------|--|--|

| Cache Type                           | What Cached             | Where Cached           | Latency<br>(cycles) | Managed<br>By       |  |  |

| Registers                            | 4-byte word             | CPU registers          | 0                   | Compiler            |  |  |

| TLB                                  | Address<br>translations | On-Chip TLB            | 0                   | Hardware            |  |  |

| L1 cache                             | 32-byte block           | On-Chip L1             | 1                   | Hardware            |  |  |

| L2 cache                             | 32-byte block           | Off-Chip L2            | 10                  | Hardware            |  |  |

| Virtual<br>Memory                    | 4-KB page               | Main memory            | 100                 | Hardware+<br>OS     |  |  |

| Buffer cache                         | Parts of files          | Main memory            | 100                 | OS                  |  |  |

| Network buffer<br>cache              | Parts of files          | Local disk             | 10,000,000          | AFS/NFS<br>client   |  |  |

| Browser cache                        | Web pages               | Local disk             | 10,000,000          | Web<br>browser      |  |  |

| Web cache                            | Web pages               | Remote server<br>disks | 1,000,000,000       | Web proxy<br>server |  |  |