Towards Hardware Cybersecurity

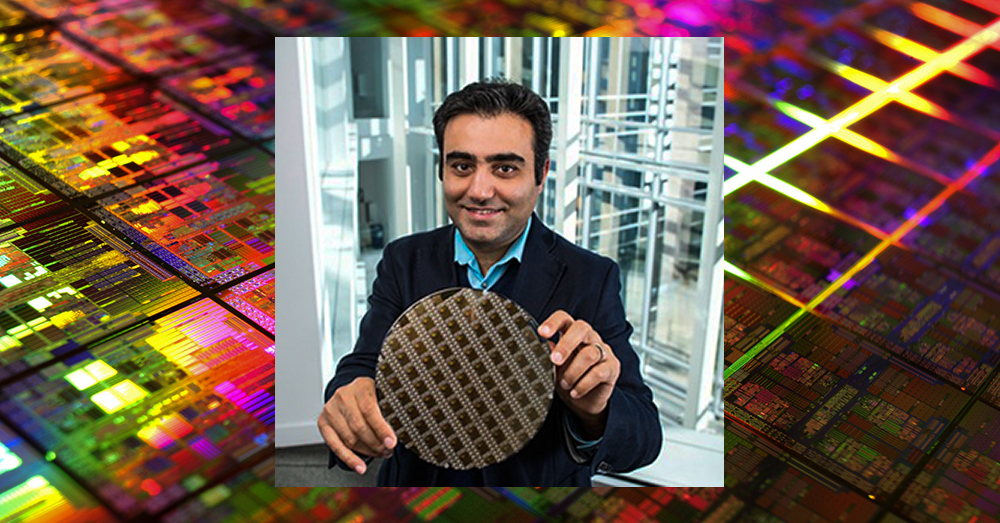

Professor Houman Homayoun

George Mason University

11:00am-12:00pm Tuesday, 20 Febuary 2018, ITE 325, UMBC

George Mason University

Electronic system security, trust and reliability has become an increasingly critical area of concern for modern society. Secure hardware systems, platforms, as well as supply chains are critical to industry and government sectors such as national defense, healthcare, transportation, and finance.

Traditionally, authenticity and integrity of data has been protected with various security protocol at the software level with the underlying hardware assumed to be secure, and reliable. This assumption however is no longer true with an increasing number of attacks reported on the hardware. Counterfeiting electronic components, inserting hardware trojans, and cloning integrated circuits are just few out of many malicious byproducts of hardware vulnerabilities, which need to be urgently addressed.

In the first part of this talk I will address the security and vulnerability challenges in the horizontal integrated hardware development process. I will then present the concept of hybrid spin-transfer torque CMOS look up table based design which is our latest effort on developing a cost-effective solution to prevent physical reverse engineering attacks.

In the second part of my talk I will present how information at the hardware level can be used to address some of the major challenges of software security vulnerabilities monitoring and detection methods. I will first discuss these challenges and will then show how the use of data at the hardware architecture level in combination with an effective machine learning based predictor helps protecting systems against various classes of hardware vulnerability attacks.

I will conclude the talk by emphasizing the importance of this emerging area and proposing a research agenda for the future.

Dr. Houman Homayoun is an Assistant Professor in the Department of Electrical and Computer Engineering at George Mason University. He also holds a courtesy appointment with the Department of Computer Science as well as Information Science and Technology Department. He is the director of GMU’s Accelerated, Secure, and Energy-Efficient Computing Laboratory (ASEEC). Prior to joining GMU, Houman spent two years at the University of California, San Diego, as NSF Computing Innovation (CI) Fellow awarded by the CRA-CCC. Houman graduated in 2010 from University of California, Irvine with a Ph.D. in Computer Science. He was a recipient of the four-year University of California, Irvine Computer Science Department chair fellowship. Houman received the MS degree in computer engineering in 2005 from University of Victoria and BS degree in electrical engineering in 2003 from Sharif University of Technology. Houman conducts research in hardware security and trust, big data computing, and heterogeneous computing, where he has published more than 80 technical papers in the prestigious conferences and journals on the subject. Since 2012 he leads ten research projects, a total of $7.2 million in funding, supported by DARPA, AFRL, NSF, NIST, and GM on the topics of hardware security and trust, big data computing, heterogeneous architectures, and biomedical computing. Houman received the 2016 GLSVLSI conference best paper award for developing a manycore accelerator for wearable biomedical computing. Since 2017 he has been serving as an Associate Editor of IEEE Transactions on VLSI. He is currently serving as technical program co-chair of 2018 GLSVLSI conference.