## UART

Universal asynchronous receiver and transmitter

## UART

• A protocol that translates data between parallel and serial form.

- Interface with PC is serial. i.e Data is sent serially, bit by bit.

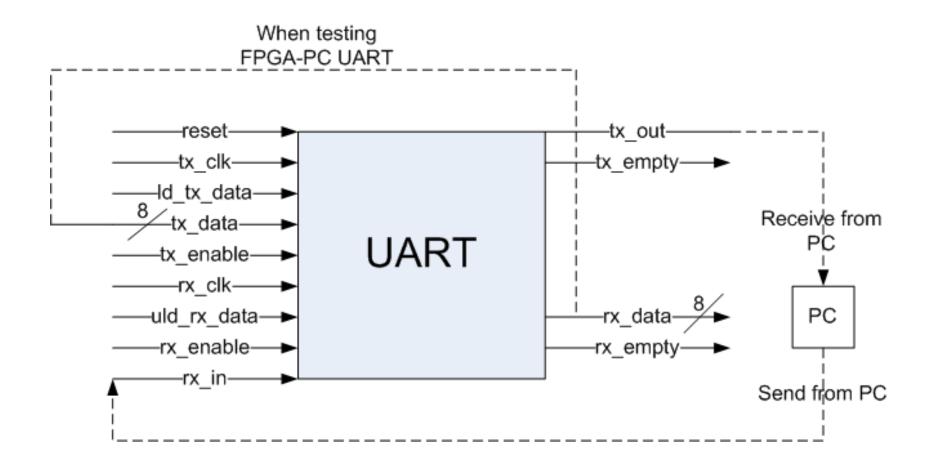

- There are only two pins between UART & PC interface: rx\_in and tx\_out.

## UART IO pins for the UART verilog example code

<u>http://www.asic-world.com/examples/verilog/uart.html</u>

## Specifics for the UART verilog example code

- For this module: rx\_clk set to be 16x faster than tx\_clk which is desired baudrate.

- Baudrate values 110, 150, 300, 1200, 2400, 9600, 19200, 38400, 115200, ...

- If tx\_empty = 1 then ld\_tx\_data = 1 => tx\_data is loaded

For receiving , check if rx\_empty = 0 then make uld\_rx\_data = 1

• For this code rx\_in = tx\_out (In test bench)

- You need to generate rx-clk and tx\_clk from a reference clk that is generated on board according to your UCF file. Tx\_clk is set as baudrate and rx-clk is 16 times faster. You need to find the appropriate counter numbers to divide the reference clk to generate both tx\_clk and rx\_clk.

- For example if reference clk is 50MhZ and the baud rate is 115200 bps. You need to divide the reference clk by 50M/115200 = 434 clock cycles to generate tx\_clk. The rx\_clk is 16 times faster, so we need to divide the reference clk by 50M/115200 /16 = 27 cycles to generate rx\_clk.

- Verilog Code example:

```

always@(posedge clk)

begin

tx counter <= tx counter + 1;</pre>

rx counter <= rx counter + 1;

if(tx counter == 434)

begin

tx counter <= 0;

txclk \leq ~txclk;

end

if(rx counter == 27)

begin

rx counter \leq 0;

rxclk <= ~ rxclk;

end

```