Digital Design: An Embedded Systems Approach Using Verilog

> Chapter 5 Memories

Portions of this work are from the book, *Digital Design: An Embedded Systems Approach Using Verilog,* by Peter J. Ashenden, published by Morgan Kaufmann Publishers, Copyright 2007 Elsevier Inc. All rights reserved.

# **General Concepts**

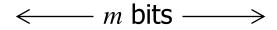

### A memory is an array of storage locations

- Each with a unique address

- Like a collection of registers, but with optimized implementation

### Address is unsigned-binary encoded

- *n* address bits  $\Rightarrow 2^n$  locations

- All locations the same size

- $2^n \times m$  bit memory

### **Memory Sizes**

- Use power-of-2 multipliers

- Kilo (K): 2<sup>10</sup> = 1,024 ≈ 10<sup>3</sup>

- Mega (M): 2<sup>20</sup> = 1,048,576 ≈ 10<sup>6</sup>

- Giga (G): 2<sup>30</sup> = 1,073,741,824 ≈ 10<sup>9</sup>

- Example

- 32K × 32-bit memory

- Capacity = 1,024K = 1Mbit

- Requires 15 address bits

- Size is determined by application requirements

# **Basic Memory Operations**

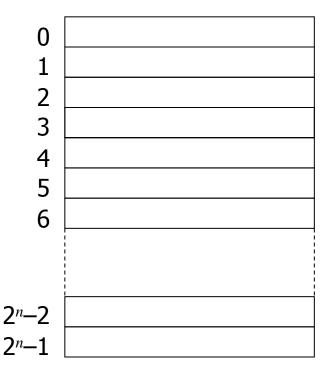

Verilog

- a inputs: unsigned address

- d\_in and d\_out

- Type depends on application

- Write operation

- en = 1, wr = 1

- d\_in value stored in location given by address inputs

- Read operation

- en = 1, wr = 0

- d\_out driven with value of location given by address inputs

- Idle: en = 0

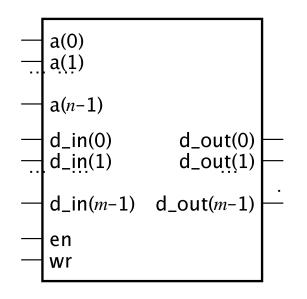

### Wider Memories

- Memory components have a fixed width

- E.g., ×1, ×4, ×8, ×16, ...

- Use memory components in parallel to make a wider memory

- E.g, three 16K×16 components for a 16K×48 memory

### More Locations

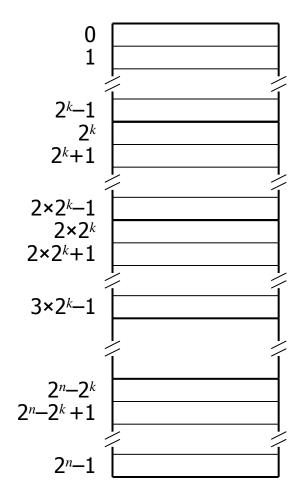

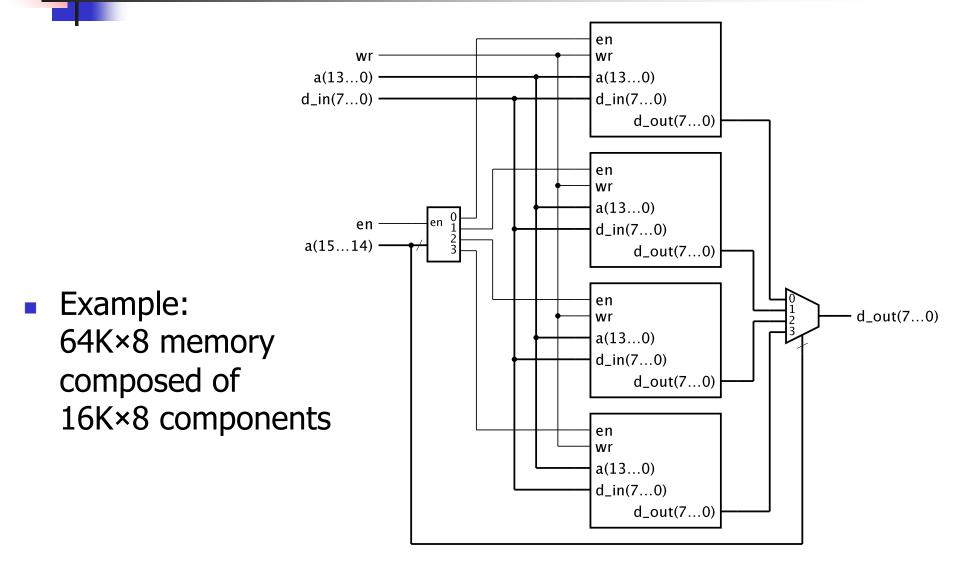

To provide 2<sup>n</sup> locations with 2<sup>k</sup>-location components • Use  $2^n/2^k$  components Address A at offset A mod 2<sup>k</sup> least-significant k bits of A • in component  $\lfloor A/2^k \rfloor$ most-significant n-k bits of A decode to select component

### More Locations

Verilog

# Memory Types

- Random-Access Memory (RAM)

- Can read and write

- Static RAM (SRAM)

- Stores data so long as power is supplied

- Asynchronous SRAM: not clocked

- Synchronous SRAM (SSRAM): clocked

- Dynamic RAM (DRAM)

- Needs to be periodically refreshed

- Read-Only Memory (ROM)

- Combinational

- Programmable and Flash rewritable

- Volatile and non-volatile

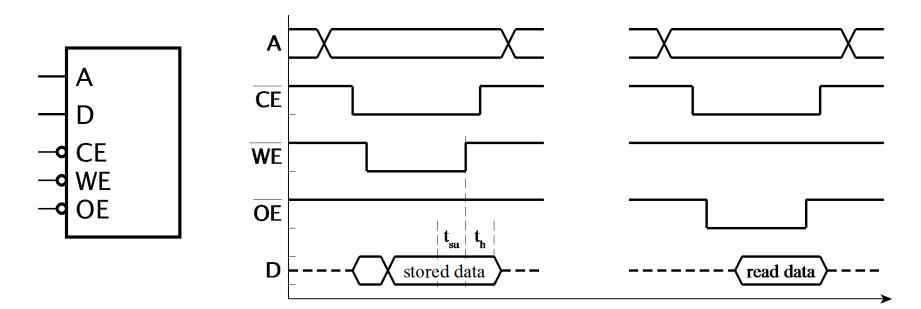

## Asynchronous SRAM

Verilog

- Data stored in 1-bit latch cells

- Address decoded to enable a given cell

- Usually use active-low control inputs

- Not available as components in ASICs or FPGAs

# Asynch SRAM Timing

- Timing parameters published in data sheets

- Access time

- From address/enable valid to data-out valid

- Cycle time

- From start to end of access

- Data setup and hold

- Before/after end of WE pulse

- Makes asynch SRAMs hard to use in clocked synchronous designs

### **Example Data Sheet**

#### CY7C1041BV33

#### Switching Characteristics<sup>[4]</sup> Over the Operating Range

| Parameter         | Description                        | -    | -12  |      | -15  |      | -17  |      |

|-------------------|------------------------------------|------|------|------|------|------|------|------|

|                   |                                    | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| READ CYCL         | E                                  | I    |      |      |      |      |      |      |

| t <sub>RC</sub>   | Read Cycle Time                    | 12   |      | 15   |      | 17   |      | ns   |

| t <sub>AA</sub>   | Address to Data Valid              |      | 12   |      | 15   |      | 17   | ns   |

| t <sub>OHA</sub>  | Data Hold from Address Change      | 3    |      | 3    |      | 3    |      | ns   |

| t <sub>ACE</sub>  | CE LOW to Data Valid               |      | 12   |      | 15   |      | 17   | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid               |      | 6    |      | 7    |      | 8    | ns   |

|                   |                                    |      |      |      |      |      |      |      |

|                   | [7 0]                              |      |      |      |      |      |      |      |

| WRITE CYCL        | .E <sup>[7, 8]</sup>               |      |      |      |      |      |      |      |

| t <sub>WC</sub>   | Write Cycle Time                   | 12   |      | 15   |      | 17   |      | ns   |

| t <sub>SCE</sub>  | CE LOW to Write End                | 10   |      | 12   |      | 12   |      | ns   |

| t <sub>AW</sub>   | Address Set-Up to Write End        | 10   |      | 12   |      | 12   |      | ns   |

| t <sub>HA</sub>   | Address Hold from Write End        | 0    |      | 0    |      | 0    |      | ns   |

| t <sub>SA</sub>   | Address Set-Up to Write Start      | 0    |      | 0    |      | 0    |      | ns   |

| t <sub>PWE</sub>  | WE Pulse Width                     | 10   |      | 12   |      | 12   |      | ns   |

| t <sub>SD</sub>   | Data Set-Up to Write End           | 7    |      | 8    |      | 9    |      | ns   |

| t <sub>HD</sub>   | Data Hold from Write End           | 0    |      | 0    |      | 0    |      | ns   |

| t <sub>LZWE</sub> | WE HIGH to Low Z <sup>[6]</sup>    | 3    |      | 3    |      | 3    |      | ns   |

| t <sub>HZWE</sub> | WE LOW to High Z <sup>[5, 6]</sup> |      | 6    |      | 7    |      | 8    | ns   |

| t <sub>BW</sub>   | Byte Enable to End of Write        | 10   |      | 12   |      | 12   |      | ns   |

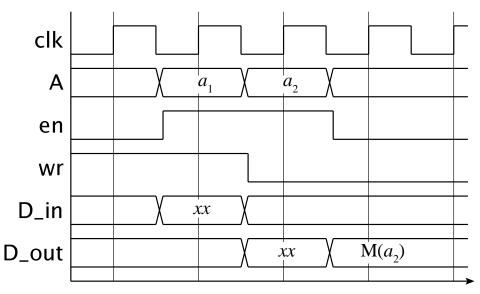

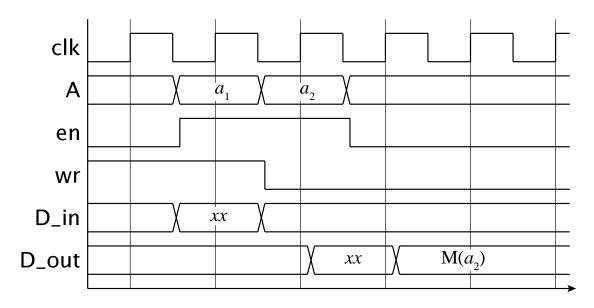

# Synchronous SRAM (SSRAM)

Clocked storage registers for inputs

address, data and control inputs

- stored on a clock edge

- held for read/write cycle

#### no register on data output

Verilog

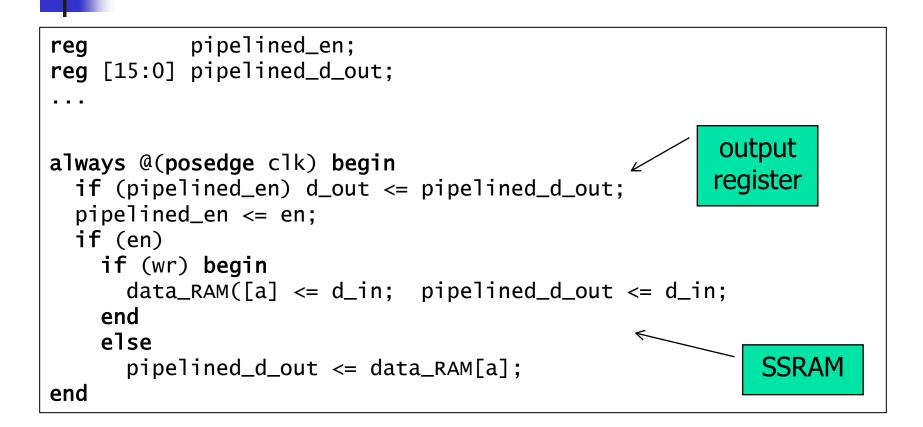

## **Pipelined SSRAM**

Verilog

- Data output also has a register

- More suitable for high-speed systems

- Access RAM in one cycle, use the data in the next cycle

```

Verilog

```

### Memories in Verilog

RAM storage represented by an array variable

```

reg [15:0] data_RAM [0:4095];

...

always @(posedge clk)

if (en)

if (wr) begin

data_RAM[a] <= d_in; d_out <= d_in;

end

else

d_out <= data_RAM[a];</pre>

```

### **Example: Coefficient Multiplier**

Verilog

```

module scaled_square ( output reg signed [7:-12] y,

input

signed [7:-12] c_in, x,

[11:0] i,

input

input

start,

input

clk. reset ):

wire

c_ram_wr;

c_ram_en, x_ce, mult_sel, y_ce;

reg

reg signed [7:-12] c_out, x_out;

reg signed [7:-12] c_RAM [0:4095];

reg signed [7:-12] operand1, operand2;

parameter [1:0] step1 = 2'b00, step2 = 2'b01, step3 = 2'b10;

[1:0] current_state, next_state;

rea

assign c_ram_wr = 1'b0;

```

## **Example: Coefficient Multiplier**

```

always @(posedge clk) // c RAM - flow through

if (c_ram_en)

if (c_ram_wr) begin

c_RAM[i] <= c_in;

c_out <= c_in;

end

else

c_out <= c_RAM[i];</pre>

always @(posedge clk) // y register

if (y_ce) begin

if (!mult_sel) begin

operand1 = c_out;

operand2 = x_out;

end

else begin

operand1 = x_out;

operand2 = y;

end

y \ll 0 operand1 * operand2;

end

```

# **Example: Coefficient Multiplier**

```

always @(posedge clk) // State register

...

always @* // Next-state logic

...

always @* begin // Output logic

...

endmodule

```

### Pipelined SSRAM in Verilog

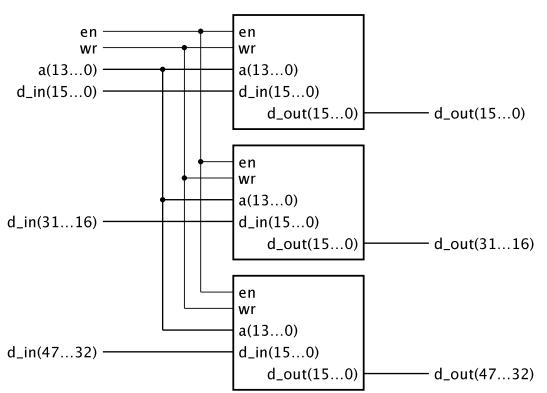

### Example: RAM Core Generator

| 💐 Block Memory Generator v1.1                                                                                                                                                                                                                                                                                                                                              | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| logi <del>CõRE</del> Blo                                                                                                                                                                                                                                                                                                                                                   | ock Memory Generator v1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ADDRA[13:0] $\rightarrow$ [23:0]DOUTA<br>DINA[23:0] $\rightarrow$<br>ENA $\rightarrow$<br>REGCEA $\rightarrow$<br>WEA[0:0] $\rightarrow$<br>SSRA $\rightarrow$<br>CLKA $\rightarrow$<br>ADDRB[16:0] $\rightarrow$ [2:0]DOUTB<br>DINB[2:0] $\rightarrow$<br>ENB $\rightarrow$<br>REGCEB $\rightarrow$<br>WEB[0:0] $\rightarrow$<br>SSRB $\rightarrow$<br>CLKB $\rightarrow$ | Pot A Options         Memory Size         Write Width       24         Range: 11152       Read Width         Write Depth       4192         Range: 89011200       Read Depth: 4192         Operating Mode       Enable         • Write First       • Always Enabled         • Read First       • Use ENA Pin         • No Change       • Use ENA Pin         • Output Reset       • Output Reset Value (Hex)         • Use SSRA Pin (set/reset pin)       • Use SSRA Pin (set/reset pin) |

| View Data Sheet                                                                                                                                                                                                                                                                                                                                                            | Page 2 of 4          Page 2 of 4                                                                                                                                                                                                                                                                                                                                                                                                                                                         |