<- previous index next ->

A "bus" is just a number of wires in parallel used to transfer

information from one device to another device. The wires may

be built into a printed wiring board, PWB, or may be in

a flexible cable.

The most important specification for a bus is its protocol.

The protocol defines the method for accessing the bus, read

requests, write requests, address and data sequencing, etc.

There may be many devices on a bus. In order for all the

devices to work together, all must follow the protocol.

A possible bus may have the following sets of lines.

The Control lines are used to implement the protocol.

There may be a bus master, hardware, that arbitrates when

two devices want to get on the bus at the same time.

When a bus has a clock, the bus is called synchronous.

All signals change on rising edge, falling edge or both.

An asynchronous bus is driven at the speed of the device

currently driving the bus.

Diagram showing how busses might be connected in a computer:

The Control lines are used to implement the protocol.

There may be a bus master, hardware, that arbitrates when

two devices want to get on the bus at the same time.

When a bus has a clock, the bus is called synchronous.

All signals change on rising edge, falling edge or both.

An asynchronous bus is driven at the speed of the device

currently driving the bus.

Diagram showing how busses might be connected in a computer:

The bandwidth, speed, of a bus may be measured in

bits per second, bps Mbps is 10^6 bps, not 2^20 bps

bytes per second, Bps communication is typically powers of 10

megahertz, MHz

words per second

transactions per second

A transaction is a complete protocol sequence.

An example with time progressing down:

Device 1 Device 2

wait for bus available

put address on bus

set request to 1

wait for Ack = 1, acknowledge

wake up because request = 1

save address from bus

set Ack to 1

wait for request = 0

wake up because Ack = 1

release address lines

set request to 0

wait for ready = 1

wake up because request = 0

set Ack to 0

put data on the bus

set ready to 1

wait for Ack = 1

wake up because ready = 1

save data from bus

set Ack to 1

wait for ready = 0

wake up because Ack = 1

release data lines

set ready to 0

finished this transaction

wake up because ready = 0

set Ack to 0

finished this transaction

bus is available

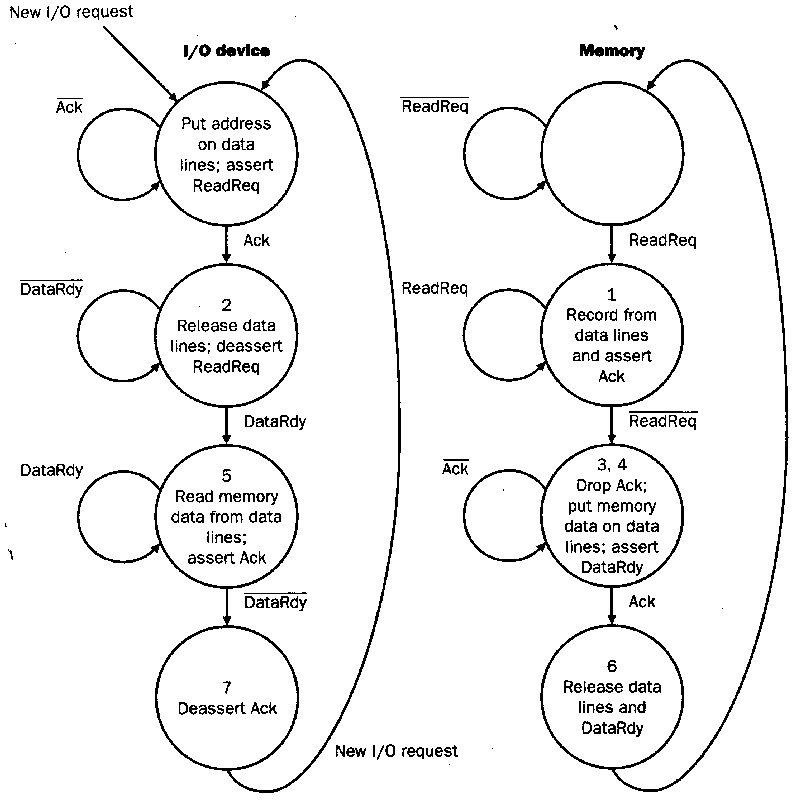

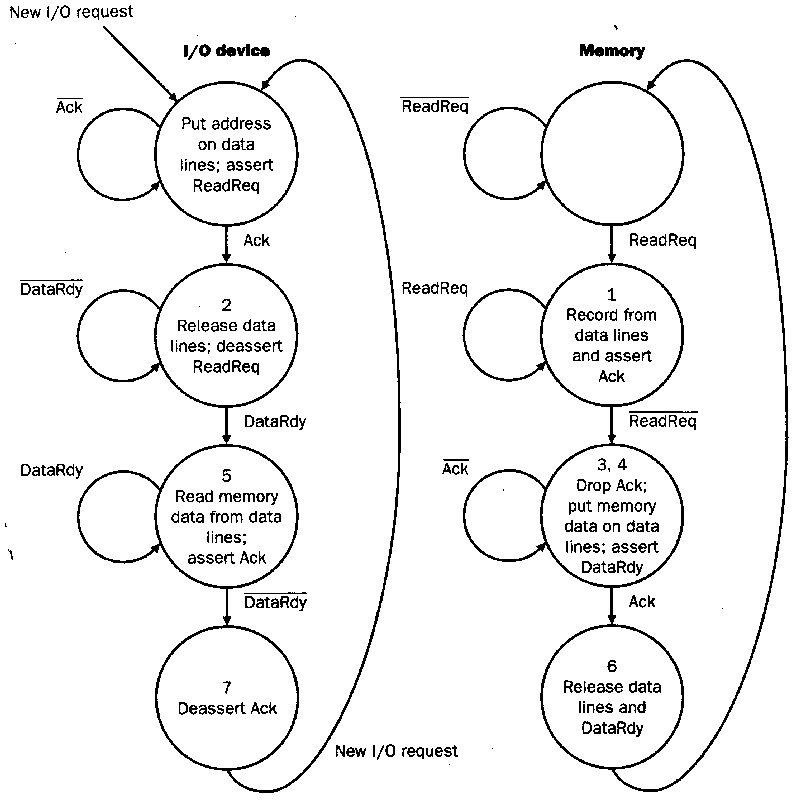

Often, the bus protocol is implemented as a Deterministic Finite

Automata, DFA. The state diagram for the above protocol could be

shown as:

The bandwidth, speed, of a bus may be measured in

bits per second, bps Mbps is 10^6 bps, not 2^20 bps

bytes per second, Bps communication is typically powers of 10

megahertz, MHz

words per second

transactions per second

A transaction is a complete protocol sequence.

An example with time progressing down:

Device 1 Device 2

wait for bus available

put address on bus

set request to 1

wait for Ack = 1, acknowledge

wake up because request = 1

save address from bus

set Ack to 1

wait for request = 0

wake up because Ack = 1

release address lines

set request to 0

wait for ready = 1

wake up because request = 0

set Ack to 0

put data on the bus

set ready to 1

wait for Ack = 1

wake up because ready = 1

save data from bus

set Ack to 1

wait for ready = 0

wake up because Ack = 1

release data lines

set ready to 0

finished this transaction

wake up because ready = 0

set Ack to 0

finished this transaction

bus is available

Often, the bus protocol is implemented as a Deterministic Finite

Automata, DFA. The state diagram for the above protocol could be

shown as:

Examples of Busses circa 2012 including older (changes with time)

Bus name Max Max Max width comment

Mbits MBytes MHz

per sec per sec

front side 17,024 2,128 133 128 many possible

34,048 4,256 133 256

19,200 2,400 150 128

85,248 10,656 333 256

136,448 17,056 533 256

204,800 25,600 800 256

225,280 26,160 880 256

256,000 32,000 1,000 256

320,000 40,000 1,250 256 (PPC Mac G5)

307,200 38,400 1,600 192 (I7 extreme, 1 channel)

AGP 2,112 264 66 32

AGP8X 17,056 2,132 533 32

PCI 1,056 132 33 32

PCI 2,112 264 33 64

PCI 2,112 264 66 32

PCI 4,224 528 66 64

PCI 4,224 528 133 32

PCI 8,448 1,056 133 64

PCIX 17,056 2,132 533 32 extended, compatible

PCIe 64,000 8,000 2000 32 express, one way, full duplex

1,2,4,8,12,16 or 32 lanes

ATA 100 800 100 25 32

ATA 133 1064 133 33 32

ATA 160 1280 160 40 32

SATA 150 1200 150 600 2 one way, full duplex

SATA std 1500 187 1500 1 one way, full duplex

limited by motherboard

SATA II 300 2400 300 1200 2

SATA II std 3000 375 3000 1 no forcing to build standard

SATA 3.0 6000 750 6000 1

SCSI 1 40 5 5 8

SCSI 2 160 20 10 16

SCSI 3 1280 160 80 16

SCSI UW3 2560 320 160 16

SCSI 320 5120 640 320 16 has cable terminators

Firewire1394 400 50 400 1

Firewire1394b 800 100 800 1 many video cameras

Firewire S16 1600 200 1600 1

Firewire S32 3200 400 3200 1

Firewire S80 6400 800 6400 1

USB 1.1 12 1.5 12 1 slow

USB 2 480 60 480 1 new cable

USB 3 3200 400 1600 2 new cable, dual differential

5000 625 2500 2 new connectors, optional speed

6400 800 3200 2 micro, mini, connectors etc.

Fiberchannel 1000 125 1000 1 1062.5

Fiberchannel 2000 250 2000 1 >mile

Fibre 16GFC 3200 14000 full duplex 10Km

Fibre 20GFC 5100 21000 full duplex

Ethernet 10 10 1.25 10 1

Ethernet 100 100 12.5 100 1

Ethernet 1Gig 1000 125 1000 1

Ethernet 10G 10000 1,250 10000 1

ISA 400 50 25 16 really old

IEEE 1284 ECP 2.5 0.31 0.31 8 half duplex

printer port

V.90 56 0.056 0.005 0.056 1 modem, one way, full duplex

OC-48 2,500 optical cross country

OC-192 STM64 10,000 Optical Carrier

OC-768 STM256 40,000 5,000 light

Mbps MBps MHz

The speed of light limits the amount of information that can be

sent over a given distance. Many busses have length restrictions.

Light can travel about

300,000,000 meters per second

300,000 meters per millisecond

300 meters per microsecond

0.3 meters per nanosecond (about 1 foot)

Unchanged in last few decades. (slower inside integrated circuit)

Pentium 4 busses and PCI-X vs PCIe

Note one example of AGP being replaced by PCI-e and the mention

of many "busses" in the advertisement:

Examples of Busses circa 2012 including older (changes with time)

Bus name Max Max Max width comment

Mbits MBytes MHz

per sec per sec

front side 17,024 2,128 133 128 many possible

34,048 4,256 133 256

19,200 2,400 150 128

85,248 10,656 333 256

136,448 17,056 533 256

204,800 25,600 800 256

225,280 26,160 880 256

256,000 32,000 1,000 256

320,000 40,000 1,250 256 (PPC Mac G5)

307,200 38,400 1,600 192 (I7 extreme, 1 channel)

AGP 2,112 264 66 32

AGP8X 17,056 2,132 533 32

PCI 1,056 132 33 32

PCI 2,112 264 33 64

PCI 2,112 264 66 32

PCI 4,224 528 66 64

PCI 4,224 528 133 32

PCI 8,448 1,056 133 64

PCIX 17,056 2,132 533 32 extended, compatible

PCIe 64,000 8,000 2000 32 express, one way, full duplex

1,2,4,8,12,16 or 32 lanes

ATA 100 800 100 25 32

ATA 133 1064 133 33 32

ATA 160 1280 160 40 32

SATA 150 1200 150 600 2 one way, full duplex

SATA std 1500 187 1500 1 one way, full duplex

limited by motherboard

SATA II 300 2400 300 1200 2

SATA II std 3000 375 3000 1 no forcing to build standard

SATA 3.0 6000 750 6000 1

SCSI 1 40 5 5 8

SCSI 2 160 20 10 16

SCSI 3 1280 160 80 16

SCSI UW3 2560 320 160 16

SCSI 320 5120 640 320 16 has cable terminators

Firewire1394 400 50 400 1

Firewire1394b 800 100 800 1 many video cameras

Firewire S16 1600 200 1600 1

Firewire S32 3200 400 3200 1

Firewire S80 6400 800 6400 1

USB 1.1 12 1.5 12 1 slow

USB 2 480 60 480 1 new cable

USB 3 3200 400 1600 2 new cable, dual differential

5000 625 2500 2 new connectors, optional speed

6400 800 3200 2 micro, mini, connectors etc.

Fiberchannel 1000 125 1000 1 1062.5

Fiberchannel 2000 250 2000 1 >mile

Fibre 16GFC 3200 14000 full duplex 10Km

Fibre 20GFC 5100 21000 full duplex

Ethernet 10 10 1.25 10 1

Ethernet 100 100 12.5 100 1

Ethernet 1Gig 1000 125 1000 1

Ethernet 10G 10000 1,250 10000 1

ISA 400 50 25 16 really old

IEEE 1284 ECP 2.5 0.31 0.31 8 half duplex

printer port

V.90 56 0.056 0.005 0.056 1 modem, one way, full duplex

OC-48 2,500 optical cross country

OC-192 STM64 10,000 Optical Carrier

OC-768 STM256 40,000 5,000 light

Mbps MBps MHz

The speed of light limits the amount of information that can be

sent over a given distance. Many busses have length restrictions.

Light can travel about

300,000,000 meters per second

300,000 meters per millisecond

300 meters per microsecond

0.3 meters per nanosecond (about 1 foot)

Unchanged in last few decades. (slower inside integrated circuit)

Pentium 4 busses and PCI-X vs PCIe

Note one example of AGP being replaced by PCI-e and the mention

of many "busses" in the advertisement:

SCSI and printer port, wave forms

For HW12, read the directions carefully. Every bus is different.

Example of HW12 solution method

Now you can do HW 12

SCSI and printer port, wave forms

For HW12, read the directions carefully. Every bus is different.

Example of HW12 solution method

Now you can do HW 12

<- previous index next ->

The Control lines are used to implement the protocol.

There may be a bus master, hardware, that arbitrates when

two devices want to get on the bus at the same time.

When a bus has a clock, the bus is called synchronous.

All signals change on rising edge, falling edge or both.

An asynchronous bus is driven at the speed of the device

currently driving the bus.

Diagram showing how busses might be connected in a computer:

The Control lines are used to implement the protocol.

There may be a bus master, hardware, that arbitrates when

two devices want to get on the bus at the same time.

When a bus has a clock, the bus is called synchronous.

All signals change on rising edge, falling edge or both.

An asynchronous bus is driven at the speed of the device

currently driving the bus.

Diagram showing how busses might be connected in a computer:

The bandwidth, speed, of a bus may be measured in

bits per second, bps Mbps is 10^6 bps, not 2^20 bps

bytes per second, Bps communication is typically powers of 10

megahertz, MHz

words per second

transactions per second

A transaction is a complete protocol sequence.

An example with time progressing down:

Device 1 Device 2

wait for bus available

put address on bus

set request to 1

wait for Ack = 1, acknowledge

wake up because request = 1

save address from bus

set Ack to 1

wait for request = 0

wake up because Ack = 1

release address lines

set request to 0

wait for ready = 1

wake up because request = 0

set Ack to 0

put data on the bus

set ready to 1

wait for Ack = 1

wake up because ready = 1

save data from bus

set Ack to 1

wait for ready = 0

wake up because Ack = 1

release data lines

set ready to 0

finished this transaction

wake up because ready = 0

set Ack to 0

finished this transaction

bus is available

Often, the bus protocol is implemented as a Deterministic Finite

Automata, DFA. The state diagram for the above protocol could be

shown as:

The bandwidth, speed, of a bus may be measured in

bits per second, bps Mbps is 10^6 bps, not 2^20 bps

bytes per second, Bps communication is typically powers of 10

megahertz, MHz

words per second

transactions per second

A transaction is a complete protocol sequence.

An example with time progressing down:

Device 1 Device 2

wait for bus available

put address on bus

set request to 1

wait for Ack = 1, acknowledge

wake up because request = 1

save address from bus

set Ack to 1

wait for request = 0

wake up because Ack = 1

release address lines

set request to 0

wait for ready = 1

wake up because request = 0

set Ack to 0

put data on the bus

set ready to 1

wait for Ack = 1

wake up because ready = 1

save data from bus

set Ack to 1

wait for ready = 0

wake up because Ack = 1

release data lines

set ready to 0

finished this transaction

wake up because ready = 0

set Ack to 0

finished this transaction

bus is available

Often, the bus protocol is implemented as a Deterministic Finite

Automata, DFA. The state diagram for the above protocol could be

shown as:

Examples of Busses circa 2012 including older (changes with time)

Bus name Max Max Max width comment

Mbits MBytes MHz

per sec per sec

front side 17,024 2,128 133 128 many possible

34,048 4,256 133 256

19,200 2,400 150 128

85,248 10,656 333 256

136,448 17,056 533 256

204,800 25,600 800 256

225,280 26,160 880 256

256,000 32,000 1,000 256

320,000 40,000 1,250 256 (PPC Mac G5)

307,200 38,400 1,600 192 (I7 extreme, 1 channel)

AGP 2,112 264 66 32

AGP8X 17,056 2,132 533 32

PCI 1,056 132 33 32

PCI 2,112 264 33 64

PCI 2,112 264 66 32

PCI 4,224 528 66 64

PCI 4,224 528 133 32

PCI 8,448 1,056 133 64

PCIX 17,056 2,132 533 32 extended, compatible

PCIe 64,000 8,000 2000 32 express, one way, full duplex

1,2,4,8,12,16 or 32 lanes

ATA 100 800 100 25 32

ATA 133 1064 133 33 32

ATA 160 1280 160 40 32

SATA 150 1200 150 600 2 one way, full duplex

SATA std 1500 187 1500 1 one way, full duplex

limited by motherboard

SATA II 300 2400 300 1200 2

SATA II std 3000 375 3000 1 no forcing to build standard

SATA 3.0 6000 750 6000 1

SCSI 1 40 5 5 8

SCSI 2 160 20 10 16

SCSI 3 1280 160 80 16

SCSI UW3 2560 320 160 16

SCSI 320 5120 640 320 16 has cable terminators

Firewire1394 400 50 400 1

Firewire1394b 800 100 800 1 many video cameras

Firewire S16 1600 200 1600 1

Firewire S32 3200 400 3200 1

Firewire S80 6400 800 6400 1

USB 1.1 12 1.5 12 1 slow

USB 2 480 60 480 1 new cable

USB 3 3200 400 1600 2 new cable, dual differential

5000 625 2500 2 new connectors, optional speed

6400 800 3200 2 micro, mini, connectors etc.

Fiberchannel 1000 125 1000 1 1062.5

Fiberchannel 2000 250 2000 1 >mile

Fibre 16GFC 3200 14000 full duplex 10Km

Fibre 20GFC 5100 21000 full duplex

Ethernet 10 10 1.25 10 1

Ethernet 100 100 12.5 100 1

Ethernet 1Gig 1000 125 1000 1

Ethernet 10G 10000 1,250 10000 1

ISA 400 50 25 16 really old

IEEE 1284 ECP 2.5 0.31 0.31 8 half duplex

printer port

V.90 56 0.056 0.005 0.056 1 modem, one way, full duplex

OC-48 2,500 optical cross country

OC-192 STM64 10,000 Optical Carrier

OC-768 STM256 40,000 5,000 light

Mbps MBps MHz

The speed of light limits the amount of information that can be

sent over a given distance. Many busses have length restrictions.

Light can travel about

300,000,000 meters per second

300,000 meters per millisecond

300 meters per microsecond

0.3 meters per nanosecond (about 1 foot)

Unchanged in last few decades. (slower inside integrated circuit)

Pentium 4 busses and PCI-X vs PCIe

Note one example of AGP being replaced by PCI-e and the mention

of many "busses" in the advertisement:

Examples of Busses circa 2012 including older (changes with time)

Bus name Max Max Max width comment

Mbits MBytes MHz

per sec per sec

front side 17,024 2,128 133 128 many possible

34,048 4,256 133 256

19,200 2,400 150 128

85,248 10,656 333 256

136,448 17,056 533 256

204,800 25,600 800 256

225,280 26,160 880 256

256,000 32,000 1,000 256

320,000 40,000 1,250 256 (PPC Mac G5)

307,200 38,400 1,600 192 (I7 extreme, 1 channel)

AGP 2,112 264 66 32

AGP8X 17,056 2,132 533 32

PCI 1,056 132 33 32

PCI 2,112 264 33 64

PCI 2,112 264 66 32

PCI 4,224 528 66 64

PCI 4,224 528 133 32

PCI 8,448 1,056 133 64

PCIX 17,056 2,132 533 32 extended, compatible

PCIe 64,000 8,000 2000 32 express, one way, full duplex

1,2,4,8,12,16 or 32 lanes

ATA 100 800 100 25 32

ATA 133 1064 133 33 32

ATA 160 1280 160 40 32

SATA 150 1200 150 600 2 one way, full duplex

SATA std 1500 187 1500 1 one way, full duplex

limited by motherboard

SATA II 300 2400 300 1200 2

SATA II std 3000 375 3000 1 no forcing to build standard

SATA 3.0 6000 750 6000 1

SCSI 1 40 5 5 8

SCSI 2 160 20 10 16

SCSI 3 1280 160 80 16

SCSI UW3 2560 320 160 16

SCSI 320 5120 640 320 16 has cable terminators

Firewire1394 400 50 400 1

Firewire1394b 800 100 800 1 many video cameras

Firewire S16 1600 200 1600 1

Firewire S32 3200 400 3200 1

Firewire S80 6400 800 6400 1

USB 1.1 12 1.5 12 1 slow

USB 2 480 60 480 1 new cable

USB 3 3200 400 1600 2 new cable, dual differential

5000 625 2500 2 new connectors, optional speed

6400 800 3200 2 micro, mini, connectors etc.

Fiberchannel 1000 125 1000 1 1062.5

Fiberchannel 2000 250 2000 1 >mile

Fibre 16GFC 3200 14000 full duplex 10Km

Fibre 20GFC 5100 21000 full duplex

Ethernet 10 10 1.25 10 1

Ethernet 100 100 12.5 100 1

Ethernet 1Gig 1000 125 1000 1

Ethernet 10G 10000 1,250 10000 1

ISA 400 50 25 16 really old

IEEE 1284 ECP 2.5 0.31 0.31 8 half duplex

printer port

V.90 56 0.056 0.005 0.056 1 modem, one way, full duplex

OC-48 2,500 optical cross country

OC-192 STM64 10,000 Optical Carrier

OC-768 STM256 40,000 5,000 light

Mbps MBps MHz

The speed of light limits the amount of information that can be

sent over a given distance. Many busses have length restrictions.

Light can travel about

300,000,000 meters per second

300,000 meters per millisecond

300 meters per microsecond

0.3 meters per nanosecond (about 1 foot)

Unchanged in last few decades. (slower inside integrated circuit)

Pentium 4 busses and PCI-X vs PCIe

Note one example of AGP being replaced by PCI-e and the mention

of many "busses" in the advertisement:

SCSI and printer port, wave forms

For HW12, read the directions carefully. Every bus is different.

Example of HW12 solution method

Now you can do HW 12

SCSI and printer port, wave forms

For HW12, read the directions carefully. Every bus is different.

Example of HW12 solution method

Now you can do HW 12