### Single Electron Devices for Logic Applications

Reza M. Rad UMBC

Based on pages 425-441 of "Nanoelectronics and Information Technology", Rainer Waser

#### Introduction

Scaling down MOSFETs has been fundamental in improving the performance of ULSI circuits

Scaling of MOSFETs is entering the deep sub 50 nm regime

Quantum mechanical effects are expected to be effective in these small structure devices

#### Introduction

A new device having operation principles effective in smaller dimensions which utilizes quantum-mechanical effects

Single electron devices retain their scalability even on an atomic scale

Single electron devices will reduce the power consumption because the number of electrons transferred from voltage source to ground is limited

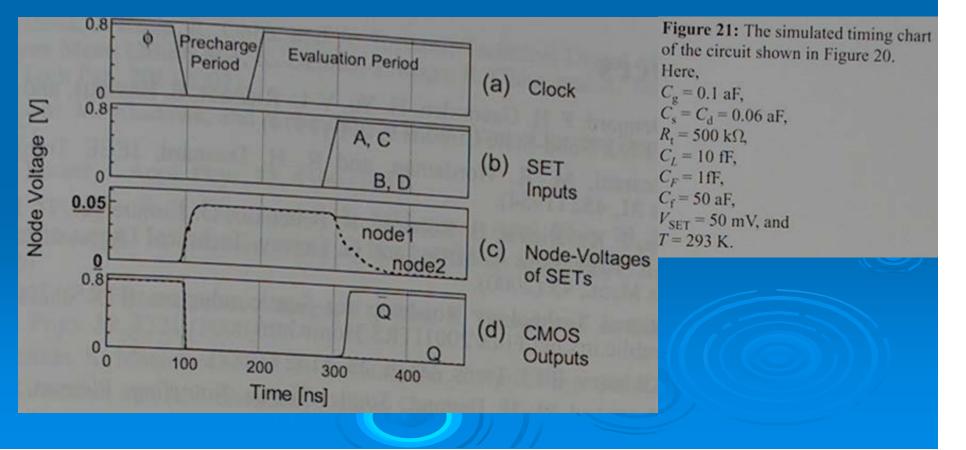

- A quantum dot connected with two electrodes

- One electrode connected to dot through a tunneling junction

- The other electrode, gate, coupled with quantum dot via insulator, electron cannot pass through tunneling

Electrons are injected/ejected to/from the dot through the tunneling junction (fig 1)

Figure 1:

(a) Schematic structure of single-electron box. The single-electron box consists of a quantum dot, an electrode connected to the dot through a tunneling junction, and an electrode coupled to the dot through an ideal, infinite-resistance, capacitor.

(b) Equivalent circuit of single-electron box.

> Basic operation of single-electron box:

- As the size of quantum dot decreases, charging energy Wc of a single excess charge on the dot increases

- If Wc is sufficiently larger than thermal energy, no electron tunnels to/from quantum dot

- Electron number in the dot takes a fixed value

- The charging effect which controls injection/ejection of a single charge to/from a quantum dot is called <u>Coulomb Blockade</u> effect

### Single Electron Devices

Condition for Coulomb blockade:

$$W_c = \frac{e^2}{2C} >> k_B T$$

- By applying a positive bias to the gate electrode we could attract an electron to the quantum dot

- Further increase of the gate voltage causes an electron to enter the dot

- In single-electron box, the electron number of the box is controlled, one by one, by utilizing the gate electrode

- Conditions for observing single-electron tunneling phenomena

- First: charging energy of a single electron to the dot must be greater than thermal energy

- Second: tunneling resistance R<sub>t</sub> of the tunneling junction must be larger than resistance quantum h/e<sup>2</sup>

- This is required to suppress the quantum fluctuations in electron number, n, of the dot

Single-electron box This condition is obtained as follows: Uncertainity principle:  $\Delta W.\Delta t > h$ let  $\Delta W$  be the charging energy of the quantum dot :  $\Delta W \approx e^2 / C$ let  $\Delta t$  be the lifetime of the charging :  $\mathbf{R}_{t}\mathbf{C}$ Then:  $(e^2 / C) \cdot \mathbf{R}_t C = e^2 R_t > h$  $R_t >> \frac{h}{\rho^2} \approx 25.8 \,\mathrm{k}\Omega$

Bias conditions for Coulomb Blockade Effects

- The voltage range which keeps electron number at n, is extracted by considering the free energy of the system

- F(n) free energy having n electrons in the island

- Wc(n) : Charging energy

- A(n) : Work done by the voltage source connected to gate in order to change the electron number from 0 to n

- Polarization charge in capacitors: due to rearrangement of electrons

$F(n) = W_c(n) - A(n)$   $Q_t - Q_g = -ne$  $\frac{Q_t}{C_t} + \frac{Q_g}{C_g} = V_g \qquad Q_t \text{ and } Q_g \text{ are the polarization}$

charge on the tunneling junction and gate capacitors

#### > Bias conditions ...

$$W_{c}(n) = \frac{Q_{t}^{2}}{2C_{t}} + \frac{Q_{g}^{2}}{2C_{g}} = \frac{e^{2}n^{2}}{2C_{\Sigma}} + \frac{1}{2}\frac{C_{t}C_{g}V_{g}^{2}}{C_{\Sigma}}, C_{\Sigma} = C_{t} + C_{g}$$

$$A(n) = \int I(t) \cdot V_{g} dt = Q_{g}V_{g} = en\frac{C_{g}}{C_{\Sigma}}V_{g} + \frac{C_{t}C_{g}V_{g}^{2}}{C_{\Sigma}}$$

To maintain electron number in quantum dot :

$$F(n) < F(n \pm 1) \Rightarrow [n - \frac{1}{2}]\frac{e}{C_{g}} < V_{g} < [n + \frac{1}{2}]\frac{e}{C_{g}}$$

#### > Bias conditions ..

Free energy change in the transition of electron number from n to n + 1:

$$\Delta F(n, n+1) = F(n+1) - F(n) = \frac{e}{C_t}(Q_t - Q_c)$$

Where:  $Q_c = \frac{e}{2} [1 + \frac{C_g}{C_t}]^{-1}$

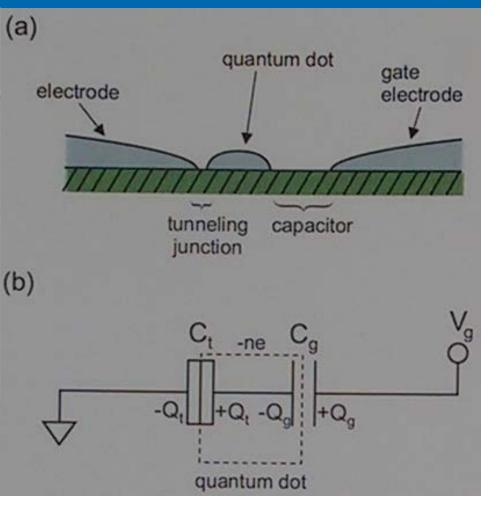

Schematic structure of a single-electron transistor (SET) is shown in the figure (fig 3)

Figure 3:

(a) Schematic structure of single-electron transistor.

(b) Equivalent circuit of single-electron transistor.

> Operation of a single-electron transistor

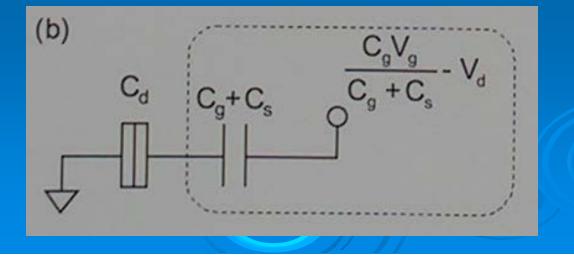

- The circuit connected to the tunneling junction of source is shown in the figure (fig4a)

- The condition for maintaining electron number at n is:

- The circuit connected to the tunneling junction of drain is transformed to the circuit shown in the figure (fig 4b)

- The condition to maintain the electron number at n is

$$\frac{1}{C_s + C_g} \left[ -ne + \frac{e}{2} + C_g V_g \right] > V_d > \frac{1}{C_s + C_g} \left[ -ne - \frac{e}{2} + C_g V_g \right]$$

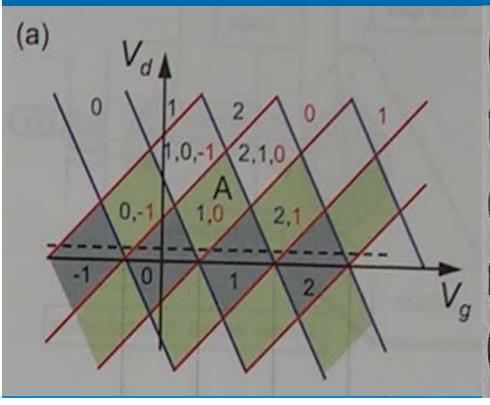

- Figure (fig 5a) shows the drain-gate voltage relation

- Gray areas are coulomb blockade areas where electron number in the dot is fixed

(a) Relationship between the drain voltage  $V_d$  and the gate voltage  $V_g$ , satisfying the conditions expressed by Eqs. (15) and (16). The diamond-shaped structure along the x-axis is called Coulomb diamond.

- Green areas are regions with two preferable electron numbers (one for source and one for drain)

- In area labeled A:

- Preferable electron number for source is 1 and for drain is 0

- Electron tunnels from source to dot to make its electron number 1

- Then it tunnels from dot to drain to change the electron number of the dot to 0

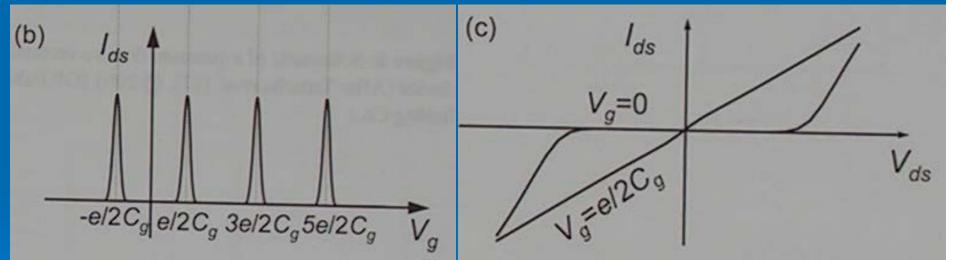

- Figure (fig 5b) shows the oscillating  $I_{ds}$  versus  $V_{a}$  characteristic of the SETs

- Typical I<sub>ds</sub> versus  $V_{ds}$  characteristics are shown in figure (fig 5c)

(b) source-to-drain current  $I_{ds}$  versus gate voltage  $V_g$  characteristics of single-electron transistors. (c)  $I_{ds}$  versus  $V_{ds}$  characteristics of single-electron transistors.

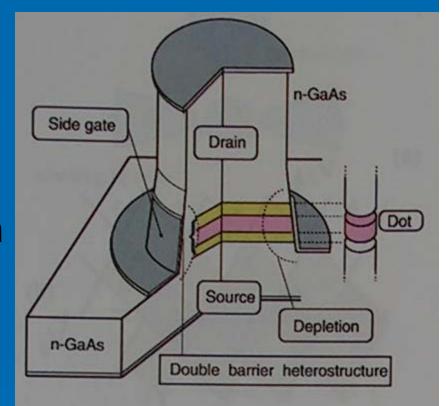

Figure (fig 6) demonstrates a implementation of a circular disk quantum dot sandwiched between source and drain and surrounding gate

Figure 6: Schematic of a quantum dot in a vertical device (After Tarucha *et al.* [17], © 2001 IOP Publishing Co.).

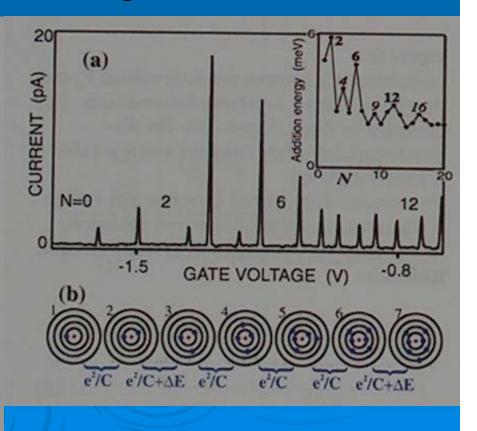

Figure (fig 7) shows Ids-Vg characteristics of the fabricated SET, inset of the figure is the electron addition energies and part b shows the energy required for adding electrons

Figure 7: Current flowing through a two dimensional circular quantum dot on varying the gate voltage.

(a) The first peak marks the voltage where the first electron enters the dot, and the number of electrons, *N*, increases by one at each subsequent peak. The distance between adjacent peaks corresponds to the addition energies (see inset).

(b) The addition of electrons to circular orbits is shown schematically. The first shell can hold two electrons whereas the second shell can contain up to four electrons. It therefore costs extra energy to add the third and seventh electrons (After Kouwenhoven *et al.* [16], © 2001 IOP Publishing Co.).

- > Advantages and disadvantages of SETs compared to MOSFETs

- SETs:

- low power consumption

- Good scalability

- Operation of SETs is limited to low temperatures

- High output impedance (Rt must be much higher than 25.8 kOhms)

- Source-drain voltage of the SETs must be smaller than the gate swing voltage

- For room temperature operation, dot must be much smaller than 10 nm, fabrication of a 10 nm structure is difficult in current technology

#### **Other Single Electron Devices**

#### > Other single electron devices

Single electron turnstile and single electron pump are devices that can control timing of single electron tunneling

Fabrication of single electron devices

- Single electron devices have been fabricated in a variety of materials such as aluminum, hetrostructures and silicon

- Fabrication on silicon is done by finelithography or by growth of silicon dots by deposition process

#### Introduction

- Many attempts have been made to develop logic circuits consisting of single electron devices

- Two approaches in logic applications:

- Representing a bit by a single electron and using single electron devices to transfer electrons one by one

- Representing a bit by more than a single electron and using single electron devices to switch the current on/off

- Former uses less power, latter results in more operation stability

> Analytical model of SET for circuit simulation

- Assumptions

- Source and drain of the SETs are connected to capacitors much larger than total capacitance of the SET island or biased by constant voltage sources

- Source and drain resistances are assumed to be the same (Rs=Rd=Rt)

- At each given gate voltage, the two most probable numbers of electrons in the SET island are taken into account

- Tunneling resistance is supposed to be much larger than quantum of resistance h/e<sup>2</sup>~25.8kOhms

Derivation of the model

I-V characteristics of SET having n or n+1 electrons is given by

$$I_{n} = \frac{e}{2R_{\Sigma}C_{\Sigma}} \frac{(\widetilde{V}_{gs,n}^{2} - \widetilde{V}_{ds}^{2})\sinh(\widetilde{V}_{ds}/\widetilde{T})}{V_{gs,n}\sinh(\widetilde{V}_{gs}/\widetilde{T}) - \widetilde{V}_{ds}\sinh(\widetilde{V}_{ds}/\widetilde{T})}$$

where

$$\widetilde{V}_{gs,n} = \frac{2C_g V_g}{e} - \frac{(C_g + C_s - C_d) V_{ds}}{e} - 1 - 2n,$$

$$\widetilde{V}_{ds} = \frac{C_{\Sigma} V_{ds}}{e}, \quad \widetilde{T} = \frac{2k_B T C_{\Sigma}}{e^2}, \quad R_{\Sigma} = R_t + R_t (R_t = R_s = R_d)$$

- It corresponds to one period of Coulomb oscillations

- Gate voltage giving peak of Coulomb oscillations is:

$$V_{gs} = \frac{e}{2C_g} + \frac{ne}{C_g} + \frac{(C_g + C_s - C_d) N_{ds}}{2C_g}$$

Considering the period of Coulomb oscillations e/Cg, gate voltage range is obtained as

$$\frac{ne}{C_g} + \frac{(C_g + C_s - C_d) N_{ds}}{2C_g} < V_{gs} < \frac{(n+1)e}{C_g} + \frac{(C_g + C_s - C_d) N_{ds}}{2C_g}$$

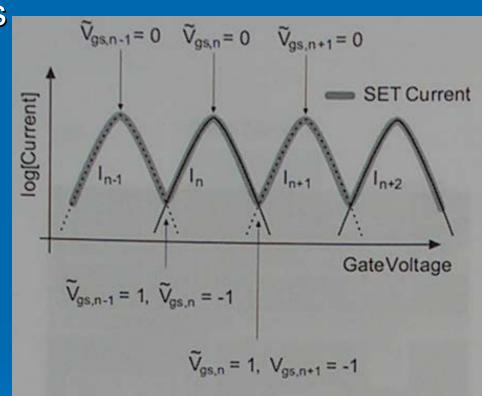

Figure (fig 13) shows coulomb oscillations over gate voltage range

**Figure 13:** Schematic of model current  $I_{n-1}, I_n, ..., I_{n+2}$  (solid and dotted lines) and SET current (thick gray line).  $I_n$  defines one period of Coulomb oscillations. The summation of  $I_n$  over a desired gate voltage range gives the Coulomb oscillations.

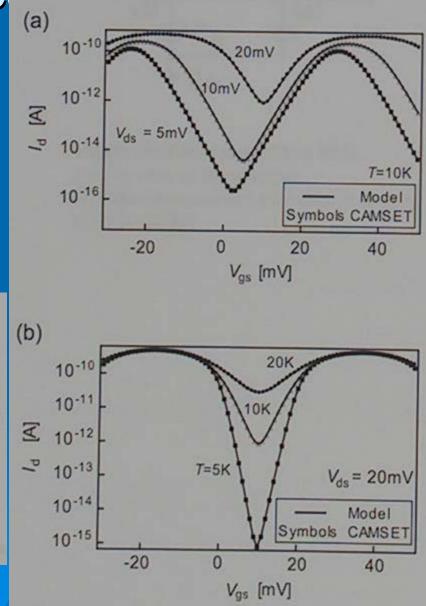

• Figure (fig 14) shows the Id-Vgs characteristics for a SET having  $C_s=C_d=1$ aF, Cg=3 aF and  $R_t=10$ MQ

Figure 14:  $I_d - V_{gs}$  characteristics of a single-electron transistor, calculated using the SET model  $I_{-1}+I_0$  (lines) and the reference simulator CAMSET (symbols) for various source-to-drain voltages (a) and temperatures (b). Here,  $C_g = 3$  aF,  $C_s = C_d = 1$  aF,  $R_t = 10$  MΩ.

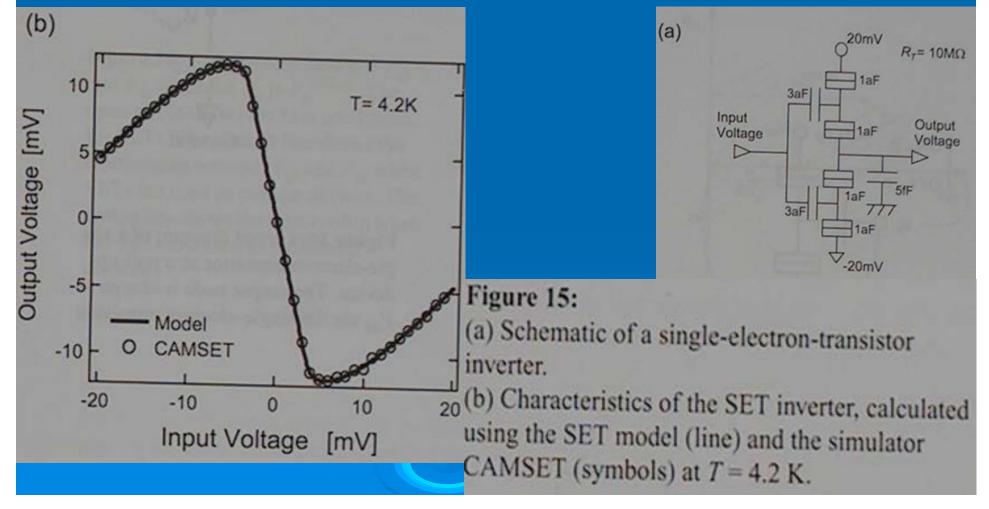

- Figure (fig 15) shows a SET inverter

- Simulations are performed using SPICE

Logic circuits with single-electron transistors

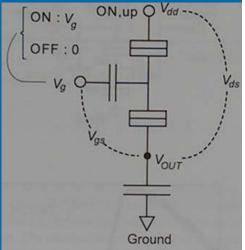

- Bias conditions for SETs (to turn SETs on)

- Figure (fig 16) shows a SET circuit where the SET is used as a pull up device

$$V_{ds} = V_{dd} - V_{OUT}, \ V_{gs} = V_g^{ON,up} - V_{OUT}$$

$$V_{gs} = V_g^{ON,up} - V_{dd} + V_{ds}$$

SETs must be turned on even at a source - drain voltage around zero, hence :

$$V_{gs} = \frac{e}{C_g} [\frac{1}{2} + n] \text{ at } V_{ds} = 0 \Longrightarrow V_g^{ON,up} = V_{dd} + \frac{e}{C_g} [\frac{1}{2} + n]$$

$$V_{gs} = V_{ds} + \frac{e}{C_g} [\frac{1}{2} + n]$$

Conditions to turn SETs off

at  $V_{gs} = 0$ ,  $V_{ds}$  is required to be :

$$-\frac{e}{2(C_g + C_s)} < V_{ds} < \frac{e}{2(C_g + C_s)}$$

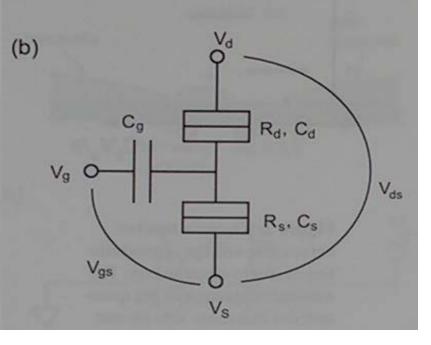

#### Design scheme

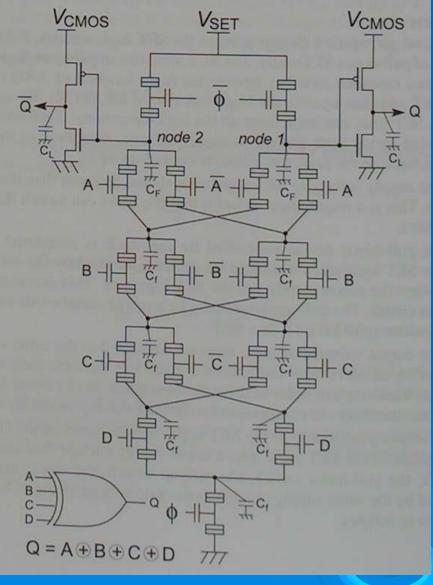

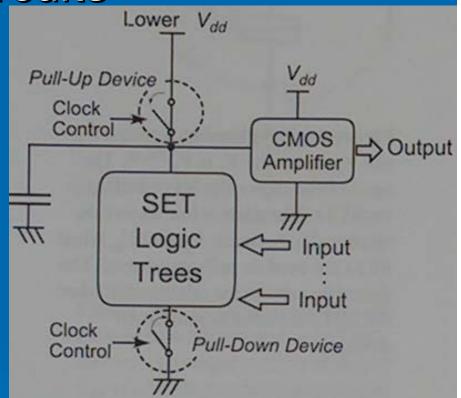

- Figure (fig 19) is a schematic of SET logic circuits

- SET logic tree consists of pull-down SETs only

- Clock Low: precharge period, load capacitor is charged regardless of inputs of SETs

- Clock High: Evaluation period, pull-down device is turned on, logic state of the output will be determined depending on the inputs

- (similar to CMOS dynamic logic)

Figure 19: Schematic of SET logic circuits described in this section. The circuit consists of the SET logic tree, a lower supply voltage than the gate voltage swing of SETs, the pull-down switch, the pull-up switch, the clock, and the CMOS amplifier biased by the same voltage as the gate voltage swing of SETs.

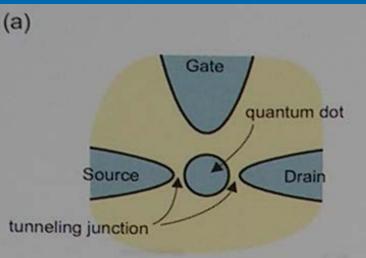

- Figure (fig 20) shows a 4-input XOR made with SETs

- Figure (fig 21) shows the simulation results