## Event Driven Simulation and Test-benches

# **Event Driven Simulation**

- Continuous time and value simulation used for analog circuits

- Differential equations should be solved

- Very slow, too much accuracy for digital circuits

# **Event Driven Simulation**

- Discrete values used for digital circuits

- '1','0','Z' and 'X' used in verilog

- This reduces the complexity of simulation

- In digital circuits event driven approach is used instead of continuous time simulation

- This also reduces complexity of simulation

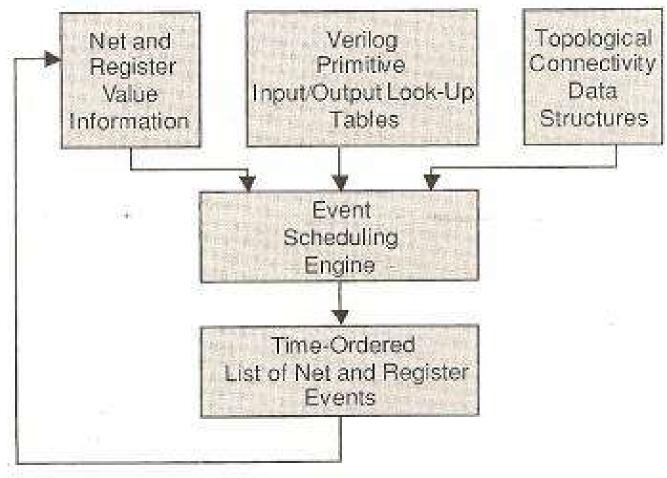

### **Event Driven Simulation**

Organization of an event-driven simulator.

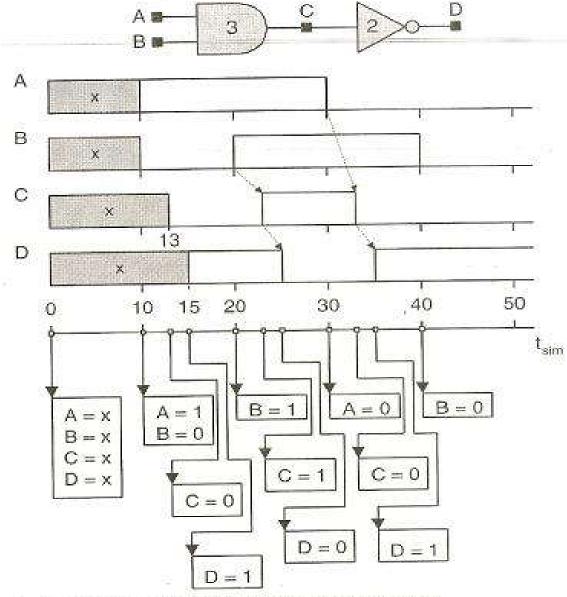

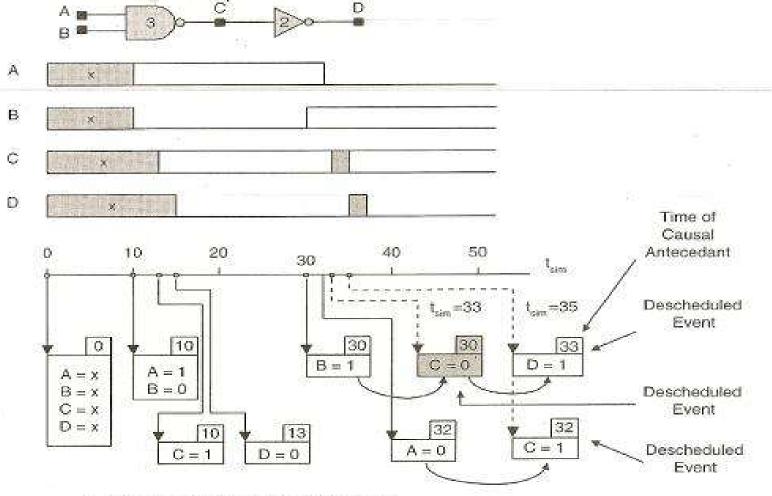

#### Example C D A Ba • Zero-delay A X B X С X D × У 40 30 50 20 10 12 î<sub>sim</sub> A = 0B = 0B = 1A = xA = 1B = xB = 0 $\mathbf{C} = \mathbf{X}$ C = 0C = 1D = x $\mathbf{C} = \mathbf{0}$ D = 0D = 1D = 1

Representation of data structures for event-driven simulation.

### Example

• Effect of delay

Data structures and event propagation delay.

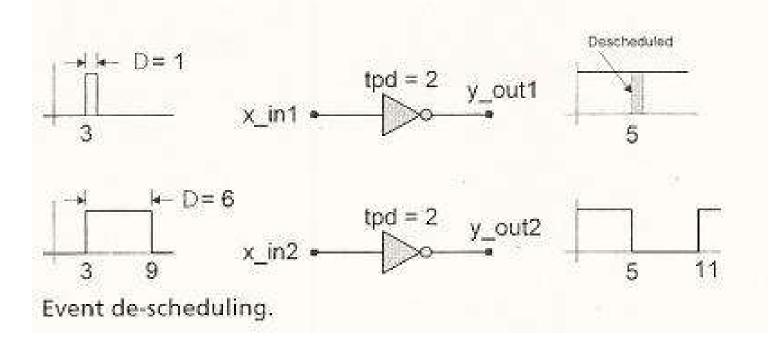

# The idea of Inertial Delay

- To model time required for charge transitions

- Close to what happens in RC circuits

### **Inertial Delay**

Verilog simulators work based on inertial delay model, event De-scheduling is required

Example of event de-scheduling.

# **Test-Benches**

• Example

| odule test_Nand_Latch_1; |                            |          | // Design Unit Testt          |                        |

|--------------------------|----------------------------|----------|-------------------------------|------------------------|

| reg                      | preset, clea               | ur;      |                               |                        |

| wire                     | q, qbar;                   |          |                               |                        |

| Nand_Lat                 | ch_1 M1 (q,                | qbar, pi | rese <mark>t</mark> , clear); | // Instantiate UUT     |

| initial                  | // Create DUTB response mo |          |                               | JTB response monitor   |

| begin                    |                            |          |                               |                        |

| \$mo                     | nitor (\$time              | , "prese | et = %b clear                 | = %b q = %b            |

| 2                        | 105                        | qbar     | = %b", prese                  | et, clear, q, qbar);   |

| end                      |                            |          |                               |                        |

| initial                  |                            |          |                               |                        |

| begin                    |                            |          | // Create DL                  | ITB stimulus generator |

| #10                      | preset                     | = 0;     | clear = 1;                    |                        |

| #10                      | preset                     | = 1;     | \$stop;                       | // Enter. to proceed   |

| #10                      | clear                      | = 0;     |                               |                        |

| #10                      | clear                      | = 1;     |                               |                        |

| #10                      | preset                     | = 0;     |                               |                        |

| end                      |                            |          |                               |                        |

| initial                  |                            |          |                               |                        |

| #60                      | \$finish ;                 |          | // Stop watcl                 | ň 👘                    |

| ndmodule                 | u rwonorostradinica        |          | 010 AD2077 AD271 073          |                        |