PhD Dissertation Proposal

Secured Embedded Many-Core Accelerator for Big Data Processing

Amey Kulkarni

2:00-4:00pm Friday, 18 September 2015, ITE 325b

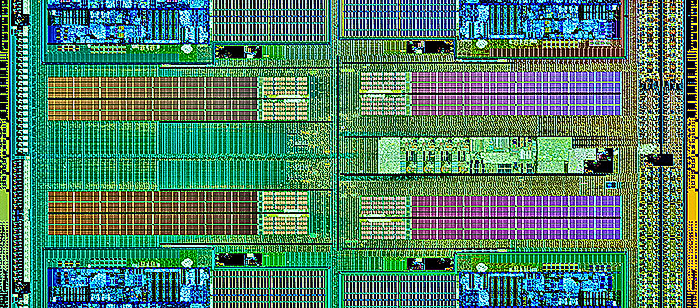

I/O bandwidth and stringent delay constraints on processing time, limits the use of streaming Big Data for a large variety of real world problems. On the other hand, examining Big Data in applications such as intelligence, surveillance and reconnaissance unveils sensitive information in terms of hidden patterns or unknown correlations, thus demanding secured processing environment. In this PhD research, we propose a scalable and secured framework for a many-core accelerator architecture for efficient big data parallel processing. We propose to merge a compressive sensing-based framework to reduce IO Bandwidth and a machine learning-based framework to secure many-core communications. Four different reduced complexity architectures and two different modifications to Orthogonal Matching Pursuit (OMP) compressive sensing reconstruction algorithm are proposed. We implement the proposed OMP architectures on FPGA, ASIC, CPU/GPU and Many-Core to investigate hardware overhead cost. To secure communications within many-core, we propose two different machine learning-based Trojan detection framework which have minimal hardware overhead. To conclude this work, we aim to implement and evaluate the proposed scalable and secured many-core accelerator hardware for image and multi-channel biomedical signal processing on quad-core and sixteen-core architectures.

Committee: Drs. Tinoosh Mohsenin, (Chair), Mohamed Younis, Seung-Jun Kim, Farinaz Koushanfar (Rice University) and Houman Homayoun (George Mason University)