MS Thesis Defense

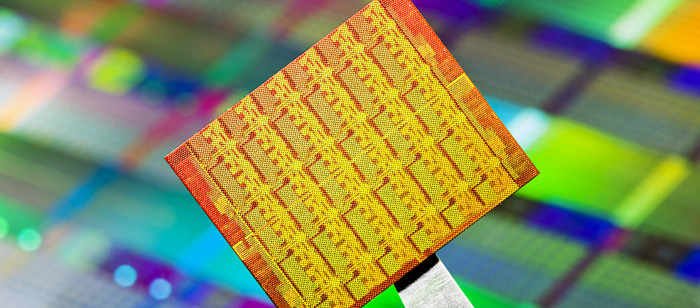

An Efficient Network on Chip (NoC) for a Low-Power,

Low-Area Homogeneous Many-Core DSP Platform

James Chandler

10:30am Monday, 30 April 30 2012, ITE 325b

This thesis presents an NoC architecture that is optimized for a course-grained, deterministic many core DSP platform supporting up to 256 cores. The proposed network supports both local and long-distance communication in the event that large applications or multiple smaller applications are mapped onto the platform by means of a hierarchical cluster topology. The NoC is designed to optimize the area- and power-to-performance ratio through implementing the following key characteristics: low hop-count long distance communication, optimized flit buffer size, efficient virtual channel implementation, and a highly restricted virtual channel flow control.

The NoC architecture is implemented in 65 nm CMOS technology with a nominal supply voltage of 1V. Place and Route results show that the proposed architecture saves up to 33% in area and up to 87.6% in energy-per-flit in comparison to some currently-implemented NoCs. Through several traffic pattern tests on a network of 16 cores, the NoC attains a throughput of up to 21.7Gbps. A 256-point FFT mapped onto 16 cores executes in 4.3$us and dissipates 0.649W. This is an improvement of 187% and 508% in latency and power dissipation over a 256-point Xilinx FFT IP Core implemented on a Virtex 6 FPGA.

Committee: Professors Tinoosh Mohsenin (chair), Dr. Chintan Patel and Mohamed Younis