[CMSC 411 Home] |

[Syllabus] |

[Project] |

[VHDL resource] |

[Homework 1-6] |

[Homework 7-12]

[Files] |

CS411 ALU for project Part1

library IEEE;

use IEEE.std_logic_1164.all;

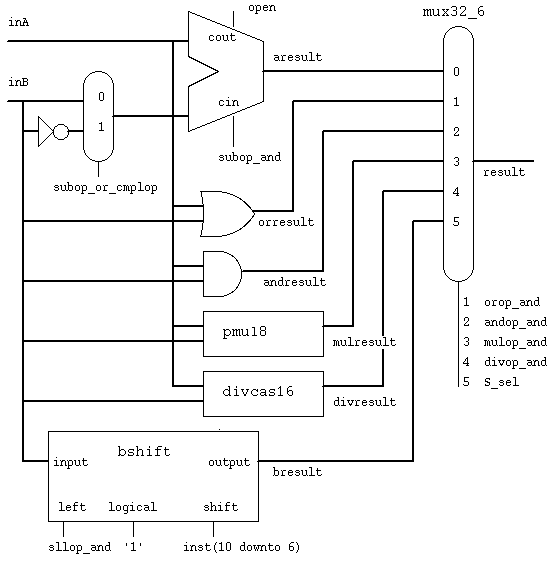

entity alu_32 is -- given. Do not change this interface

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

-- OK to paste below into your part1.vhdl after signal cout

signal S_sel : std_logic; -- S_sel <= sllop_and or srlop_and;

signal sllop : std_logic;

signal sllop_and : std_logic;

signal RRop : std_logic;

signal orop : std_logic;

signal orop_and : std_logic;

signal orresult : std_logic_vector (31 downto 0);

subop_or_cmplop : std_logic;

-- ??? many more of these 6 for and, mul, div, sub, srl, cmpl

signal bresult : std_logic_vector (31 downto 0);

-- ??? may need mode ?result the complier will tell you which are needed

begin -- schematic OK to paste below into your part1.vhdl after begin

ORR : entity WORK.equal6 port map(inst(31 downto 26), "000000", RRop);

Oor: entity WORK.equal6 port map(inst(5 downto 0), "001101", orop);

Omul: entity WORK.equal6 port map(inst(5 downto 0), "011011", mulop);

Odiv: entity WORK.equal6 port map(inst(5 downto 0), "011000", divop);

-- ??? insert other xxxop statements from cs411_opcodes.txt

orop_and <=orop and RRop;

mulop_and <=mulop and RRop;

divop_and <=divop and RRop;

subop_or_cmplop <= subop_and or cmplop_and;

-- ??? insert other xxx_and statements

bsh: entity WORK.bshift port map(left => sllop_and,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

Mul16: entity work.pmul16 port map(a => inA(15 downto 0),

b => inB(15 downto 0),

p => mulresult(31 downto 0));

Div16: entity work.divcas16 port map(dividend => inA,

divisor => inB(15 downto 0),

quotient => divresult(15 downto 0),

remainder => divrem(15 downto 0));

Omux: entity WORK.mux32_6 port map(in0=>aresult,

in1=>orresult,

in2=>andresult,

in3=>mulresult,

in4=>divresult,

in5=>bresult,

ct1=>orop_and,

ct2=>andop_and,

ct3=>mulop_and,

ct4=>divop_and,

ct5=>S_sel,

result=>result);

-- end paste

end architecture schematic; -- of alu_32

library IEEE;

use IEEE.std_logic_1164.all;

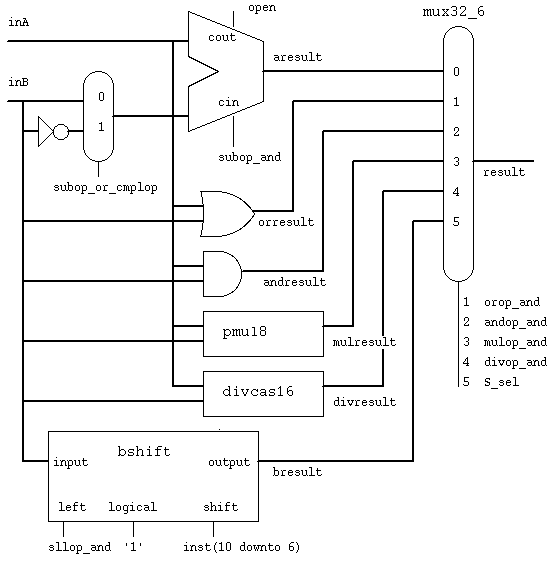

entity alu_32 is -- given. Do not change this interface

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

-- OK to paste below into your part1.vhdl after signal cout

signal S_sel : std_logic; -- S_sel <= sllop_and or srlop_and;

signal sllop : std_logic;

signal sllop_and : std_logic;

signal RRop : std_logic;

signal orop : std_logic;

signal orop_and : std_logic;

signal orresult : std_logic_vector (31 downto 0);

subop_or_cmplop : std_logic;

-- ??? many more of these 6 for and, mul, div, sub, srl, cmpl

signal bresult : std_logic_vector (31 downto 0);

-- ??? may need mode ?result the complier will tell you which are needed

begin -- schematic OK to paste below into your part1.vhdl after begin

ORR : entity WORK.equal6 port map(inst(31 downto 26), "000000", RRop);

Oor: entity WORK.equal6 port map(inst(5 downto 0), "001101", orop);

Omul: entity WORK.equal6 port map(inst(5 downto 0), "011011", mulop);

Odiv: entity WORK.equal6 port map(inst(5 downto 0), "011000", divop);

-- ??? insert other xxxop statements from cs411_opcodes.txt

orop_and <=orop and RRop;

mulop_and <=mulop and RRop;

divop_and <=divop and RRop;

subop_or_cmplop <= subop_and or cmplop_and;

-- ??? insert other xxx_and statements

bsh: entity WORK.bshift port map(left => sllop_and,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

Mul16: entity work.pmul16 port map(a => inA(15 downto 0),

b => inB(15 downto 0),

p => mulresult(31 downto 0));

Div16: entity work.divcas16 port map(dividend => inA,

divisor => inB(15 downto 0),

quotient => divresult(15 downto 0),

remainder => divrem(15 downto 0));

Omux: entity WORK.mux32_6 port map(in0=>aresult,

in1=>orresult,

in2=>andresult,

in3=>mulresult,

in4=>divresult,

in5=>bresult,

ct1=>orop_and,

ct2=>andop_and,

ct3=>mulop_and,

ct4=>divop_and,

ct5=>S_sel,

result=>result);

-- end paste

end architecture schematic; -- of alu_32

Last updated 8/23/2020

library IEEE;

use IEEE.std_logic_1164.all;

entity alu_32 is -- given. Do not change this interface

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

-- OK to paste below into your part1.vhdl after signal cout

signal S_sel : std_logic; -- S_sel <= sllop_and or srlop_and;

signal sllop : std_logic;

signal sllop_and : std_logic;

signal RRop : std_logic;

signal orop : std_logic;

signal orop_and : std_logic;

signal orresult : std_logic_vector (31 downto 0);

subop_or_cmplop : std_logic;

-- ??? many more of these 6 for and, mul, div, sub, srl, cmpl

signal bresult : std_logic_vector (31 downto 0);

-- ??? may need mode ?result the complier will tell you which are needed

begin -- schematic OK to paste below into your part1.vhdl after begin

ORR : entity WORK.equal6 port map(inst(31 downto 26), "000000", RRop);

Oor: entity WORK.equal6 port map(inst(5 downto 0), "001101", orop);

Omul: entity WORK.equal6 port map(inst(5 downto 0), "011011", mulop);

Odiv: entity WORK.equal6 port map(inst(5 downto 0), "011000", divop);

-- ??? insert other xxxop statements from cs411_opcodes.txt

orop_and <=orop and RRop;

mulop_and <=mulop and RRop;

divop_and <=divop and RRop;

subop_or_cmplop <= subop_and or cmplop_and;

-- ??? insert other xxx_and statements

bsh: entity WORK.bshift port map(left => sllop_and,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

Mul16: entity work.pmul16 port map(a => inA(15 downto 0),

b => inB(15 downto 0),

p => mulresult(31 downto 0));

Div16: entity work.divcas16 port map(dividend => inA,

divisor => inB(15 downto 0),

quotient => divresult(15 downto 0),

remainder => divrem(15 downto 0));

Omux: entity WORK.mux32_6 port map(in0=>aresult,

in1=>orresult,

in2=>andresult,

in3=>mulresult,

in4=>divresult,

in5=>bresult,

ct1=>orop_and,

ct2=>andop_and,

ct3=>mulop_and,

ct4=>divop_and,

ct5=>S_sel,

result=>result);

-- end paste

end architecture schematic; -- of alu_32

library IEEE;

use IEEE.std_logic_1164.all;

entity alu_32 is -- given. Do not change this interface

port(inA : in std_logic_vector (31 downto 0);

inB : in std_logic_vector (31 downto 0);

inst : in std_logic_vector (31 downto 0);

result : out std_logic_vector (31 downto 0));

end entity alu_32;

architecture schematic of alu_32 is

-- OK to paste below into your part1.vhdl after signal cout

signal S_sel : std_logic; -- S_sel <= sllop_and or srlop_and;

signal sllop : std_logic;

signal sllop_and : std_logic;

signal RRop : std_logic;

signal orop : std_logic;

signal orop_and : std_logic;

signal orresult : std_logic_vector (31 downto 0);

subop_or_cmplop : std_logic;

-- ??? many more of these 6 for and, mul, div, sub, srl, cmpl

signal bresult : std_logic_vector (31 downto 0);

-- ??? may need mode ?result the complier will tell you which are needed

begin -- schematic OK to paste below into your part1.vhdl after begin

ORR : entity WORK.equal6 port map(inst(31 downto 26), "000000", RRop);

Oor: entity WORK.equal6 port map(inst(5 downto 0), "001101", orop);

Omul: entity WORK.equal6 port map(inst(5 downto 0), "011011", mulop);

Odiv: entity WORK.equal6 port map(inst(5 downto 0), "011000", divop);

-- ??? insert other xxxop statements from cs411_opcodes.txt

orop_and <=orop and RRop;

mulop_and <=mulop and RRop;

divop_and <=divop and RRop;

subop_or_cmplop <= subop_and or cmplop_and;

-- ??? insert other xxx_and statements

bsh: entity WORK.bshift port map(left => sllop_and,

logical => '1',

shift => inst(10 downto 6),

input => inB,

output => bresult);

Mul16: entity work.pmul16 port map(a => inA(15 downto 0),

b => inB(15 downto 0),

p => mulresult(31 downto 0));

Div16: entity work.divcas16 port map(dividend => inA,

divisor => inB(15 downto 0),

quotient => divresult(15 downto 0),

remainder => divrem(15 downto 0));

Omux: entity WORK.mux32_6 port map(in0=>aresult,

in1=>orresult,

in2=>andresult,

in3=>mulresult,

in4=>divresult,

in5=>bresult,

ct1=>orop_and,

ct2=>andop_and,

ct3=>mulop_and,

ct4=>divop_and,

ct5=>S_sel,

result=>result);

-- end paste

end architecture schematic; -- of alu_32