## Logic Gate Delay

Chip designers need to choose:

- What is the best circuit topology for a function?

- How many stages of logic produce least delay?

- How wide transistors should be?

# Logical Effort

Helps make the above decisions. Uses a simple delay model Allows easy hand calculations Compare alternative designs easily

Express delay in process independent terms

$$d = d_{abs} / \tau$$

e.g.  $\tau = 12 \text{ ps in } 180 \text{nm}, 40 \text{ ps in } 0.6 \mu\text{m}$

Delay has two components

d = f + p where,

f = Effort Delay (stage effort) = gh

p = Parasitic Delay

# Logical Effort

I.

# Logic Gate Delay

# g logical Effort

- Measures relative ability of gate to deliver current

- 1 for inverter

# *h electrical effort* = $C_{out}/C_{in}$

- Ratio of output to input capacitance

- Sometimes called fanout

## p parasitic delay

- Represents delay of gate driving no load

- Set by internal parasitic capacitance

Again

$$d = f + p = gh + p$$

p:

$$G = 1$$

$G = 1$

$G = 1$

| Logicui Ljjon          |                                                                                           |                                  |                                                                                   |                  |                |

|------------------------|-------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------|------------------|----------------|

| Can be m               | It is the ratio of<br>livering the same<br>leasured from dete by counting                 | e output current elay vs. fanout | <i>nt</i> .<br>plots                                                              | ite to the input | capacitance of |

| $C_{in} = 3$ $g = 3/3$ | $\begin{bmatrix} 2 \\ -Y \end{bmatrix} = 4E$ $\begin{bmatrix} 1 \\ g = 4/3 \end{bmatrix}$ |                                  | $\begin{array}{c} A \\ \hline Y \\ B \\ \hline C_{in} = 3 \\ g = 5/3 \end{array}$ |                  | - Y            |

| Gate Type              | Number of Inputs                                                                          |                                  |                                                                                   |                  |                |

| Gute Type              | 1                                                                                         | 2                                | 3                                                                                 | 4                | n              |

| Inverter               | 1                                                                                         |                                  |                                                                                   |                  |                |

| NAND                   |                                                                                           | 4/3                              | 5/3                                                                               | 6/3              | (n+2)/3        |

| NOR                    |                                                                                           | 5/3                              | 7/3                                                                               | 9/3              | (2n+1)/3       |

| Tristate, Mux          | 2                                                                                         | 2                                | 2                                                                                 | 2                | 2              |

| XOR, XNOR              |                                                                                           | 4,4                              | 6,12,6                                                                            | 8,16,16,8        |                |

Principles of VLSI Design

Logical Effort

### Parasitic Delay

Count diffusion capacitance on the output assuming contacted diffusions.

- Inverter: 3 units of diffusion capacitance, parasitic delay is  $3RC = \tau$ .

- Normalized parasitic p<sub>inv</sub> is.

- p<sub>inv</sub> is the ratio of diffusion capacitance to gate capacitance for a particular process. Is considered close to 1 for simplicity

Logical Effort

- More refined parasitic delay estimations can be performed using Elmore delay. Internal diffusion capacitance are considered, delay grows quadratically rather than linearly as estimated by the crude method.

- Parasitic delay for common gates using the crude method

| Gate Type     | Number of Inputs |   |   |   |    |

|---------------|------------------|---|---|---|----|

|               | 1                | 2 | 3 | 4 | n  |

| Inverter      | 1                |   |   |   |    |

| NAND          |                  | 2 | 3 | 4 | n  |

| NOR           |                  | 2 | 3 | 4 | n  |

| Tristate, Mux | 2                | 4 | 6 | 8 | 2n |

#### AN HONORS UNIVERSITY IN MARYLAN

# Logical Effort

### Multistage Logic Networks

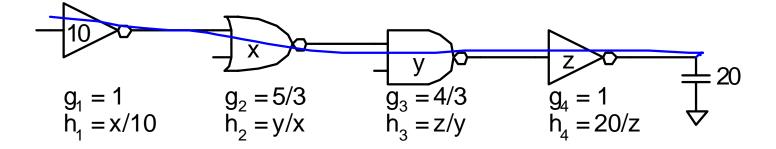

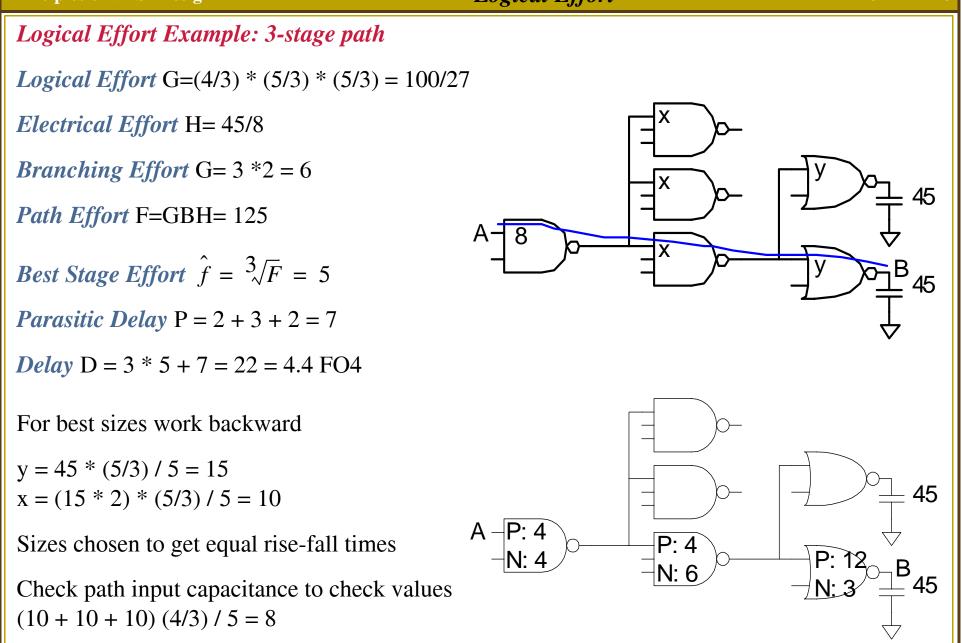

Logical Effort generalizes to multistage networks

- Path Logical Effort:  $G = \prod g_i$

- Path Electrical Effort:  $H = \frac{C_{outpath}}{C_{inpath}}$

Path Effort:  $F = \prod f_i = \prod g_i h_i$

Thus by analogy is F = GH? NO! Due to branching paths.

### Logical Effort

#### **CMPE 413**

### Multistage Logic Networks: Branching Effort

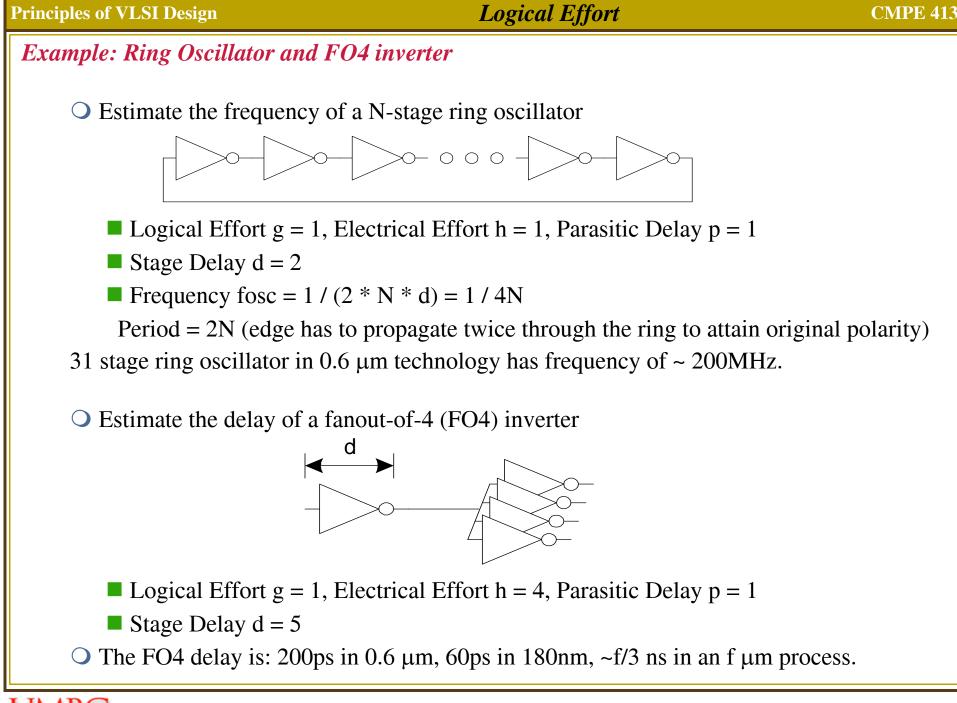

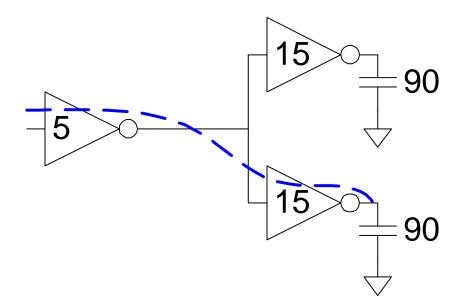

G = 1 H = 90/5 = 18 GH = 18  $h_1 = (15 + 15) / 5 = 6$   $h_2 = 90/15 = 6$  $F = g_1g_2h_1h^2 = 36 = 2GH$

Thus we need to introduce *branching effort*.

#### **CMPE 413**

### Multistage Delay

**O** Branching Effort

Accounts for branching between stages in path

$$b = \frac{C_{onpath} + C_{offpath}}{C_{onpath}}$$

$$B = \prod b_i$$

$\bigcirc$  Path Effort: F = GBH

$\bigcirc$  Path Effort Delay:  $D_F = \sum f_i$

**•** Path Parasitic Delay:  $P = \sum p_i$

$\bigcirc$  Path Delay:  $D = \sum d_i = D_F + P$

### Logical Effort

### **Designing Fast Circuits**

Delay is the smallest when each stage bears the same effort f, with N stages in the path

$$\hat{f} = g_i h_i = F^{1/N}$$

Thus, minimum delay of N stage path is

$$D = NF^{1/N} + P$$

The above equation helps to find fastest possible delay without calculating gate sizes.

Capacitance transformation used to used to calculate gate widths.

$$\hat{f} = gh = g \frac{C_{out}}{C_{in}}$$

Working backward, apply capacitance transformation to find input capacitance of each gate given load it drives

Check work by verifying input capacitance specification is met.

### Logical Effort

Logical Effort **Principles of VLSI Design CMPE 413 Best Number of Stages** Another important choice is the number of stages in a path Minimum number of stages does not provide best delay in all cases E.g. drive 64-bit datapath with unit inverter InitialDriver  $D = NF^{1/N} + P = N(64)^{1/N} + N$ 8 16 +64 + 64 **∔**64 DatapathLoad  $\pm 64$  $\stackrel{\frown}{\vdash}$  $\stackrel{\frown}{\vdash}$  $\Delta$  $\diamond$ 2 3 N: 1 8 4 15 64 2.8 f: 15.3 D: 65 18 Fastest

### Logical Effort

#### **Best Number of Stages**

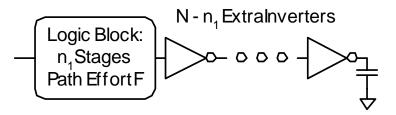

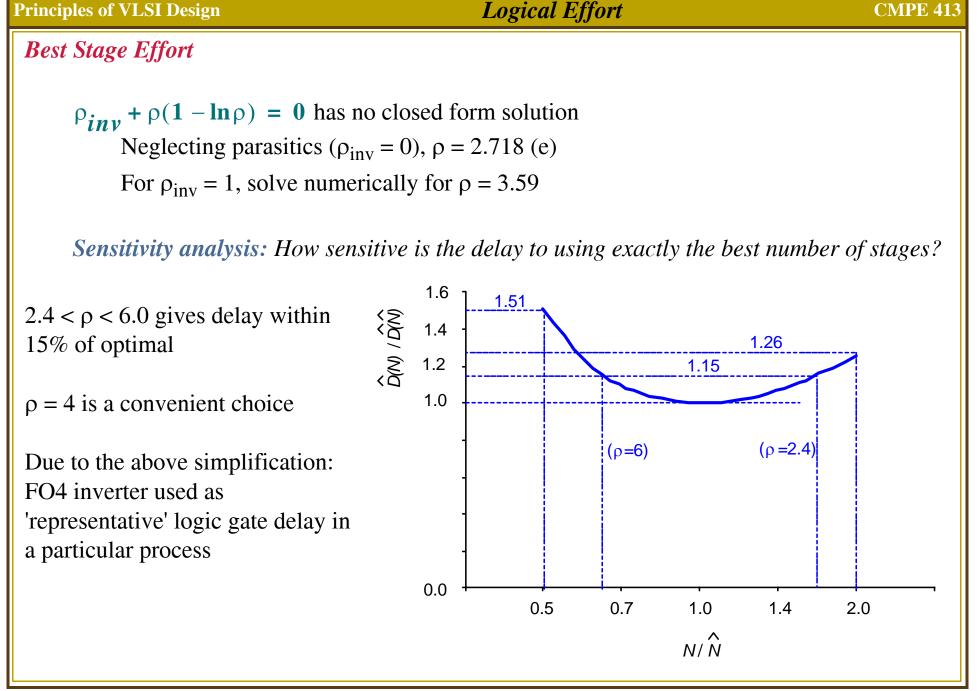

Consider adding inverters at the end of the path? How many produce the best delay?

$$D = NF^{1/N} + \sum_{i=1}^{n_1} p_i + (N - n_1)\rho_{inv}$$

$$\frac{\partial D}{\partial N} = -F^{1/N} \ln F^{1/N} + F^{1/N} + \rho_{inv} = 0$$

Define best stage effort  $\rho = F^{1/N}$

$$\rho_{inv} + \rho(1 - \ln \rho) = 0$$

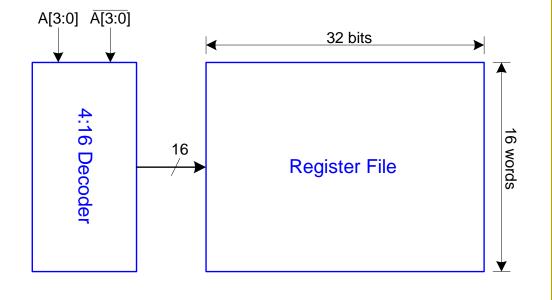

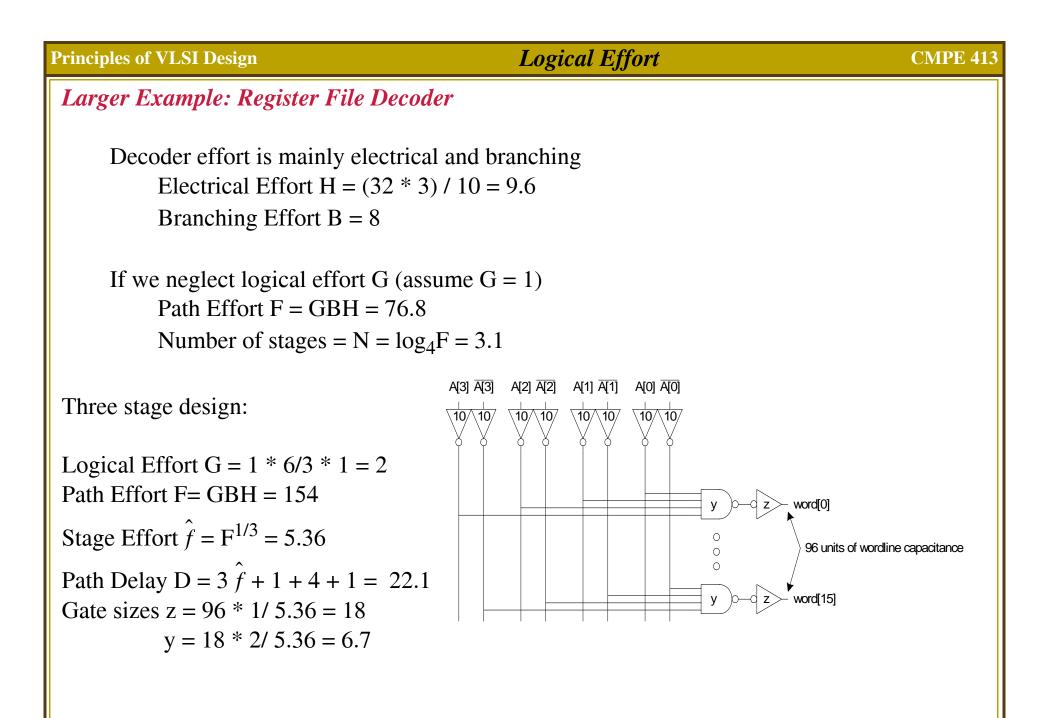

## Larger Example: Register File Decoder

Decoder specifications

- 16 word register file

- Each word is 32 bits wide

- Each bit presents a load of 3 unit-sized transistors on the word line

- True and complimentary versions of address bits A[3:0] are available

- Each address input can drive 10 unit-sized transistors.

How many stages to use?

How large should each gate be?

How fast can the decoder operate?

# Logical Effort

## Larger Example: Register File Decoder

Compare alternatives with a spreadsheet

| Design                                | Ν | G    | Р | D    |

|---------------------------------------|---|------|---|------|

| NAND4 - INV                           | 2 | 2    | 5 | 29.8 |

| NAND2 - NOR2                          | 2 | 20/9 | 4 | 30.1 |

| INV - NAND4 - INV                     | 3 | 2    | 6 | 22.1 |

| NAND4 - INV - INV - INV               | 4 | 2    | 7 | 21.1 |

| NAND2 - NOR2 - INV - INV              | 4 | 20/9 | 6 | 20.5 |

| NAND2 - INV - NAND2 - INV             | 4 | 16/9 | 6 | 19.7 |

| INV - NAND2 - INV - NAND2 - INV       | 5 | 16/9 | 7 | 20.4 |

| NAND2 - INV - NAND2 - INV - INV - INV | 6 | 16/9 | 8 | 21.6 |

| rinciples of VLSI Design | Logical Effort                                    | CMPE 4                               |

|--------------------------|---------------------------------------------------|--------------------------------------|

| Logical Effort: Recap of | Definitions                                       |                                      |

| TERM                     | STAGE                                             | PATH                                 |

| number of stages         | 1                                                 | N                                    |

| logical effort           | g                                                 | $G = \prod g_i$                      |

| electrical effort        | Cout / Cin                                        | $H = \frac{C_{outpath}}{C_{inpath}}$ |

| branching effort         | $b = \frac{C_{onpath} + C_{offpath}}{C_{onpath}}$ | $B = \prod b_i$                      |

| effort                   | f = gh                                            | F = GBH                              |

| effort delay             | f                                                 | $D_F = \sum f_i$                     |

| parasitic delay          | p                                                 | $P = \sum p_i$                       |

| delay                    | d = f + p                                         | $D = \sum d_i = D_F + P$             |

### Logical Effort

#### **CMPE 413**

#### Logical Effort: Method Recap

- $\bigcirc$  Compute path effort F = GBH

- $\bigcirc$  Estimate best number of stages  $N = log_4 F$

- Sketch path with N stages

- Estimate least delay  $D = NF^{1/N} + P$

- Determine best stage effort  $\hat{f} = F^{1/N}$

- Find gate sizes using capacitance transformation  $\hat{f} = g \frac{C_{out}}{C_{i}}$

### Logical Effort Summary

- Provides a mechanism for designing and discussing fast circuits

- NANDs are faster than NORs in CMOS

- Paths are fastest when effort delay is ~4

- Path delay is weakly sensitive to stages, sizes

- Using fewer stages doesn't mean faster circuit

- Inverters and NAND2 best for driving large loads (caps)

- BUT REQUIRES **PRACTICE** TO MASTER !!!

## Limitations of Logical Effort

- Chicken and Egg problem

Need path to compute G

But don't know number of stages without G

- Simplistic Delay Model

- Neglects input rise time effects and input arrival times Gate-source capacitance approximation

- Bootstrapping due to gate to drain capacitance coupling

- Ignores secondary effects: velocity saturation, body effect etc

- Does not account for interconnect

More applicable to datapath circuits with regular layout structure e.g. adders, mults etc Iterations required in designs with significant interconnect delay

- Design for maximum speed only, no information about minimum area/power

- Paths with complex branching are difficult to analyze by hand